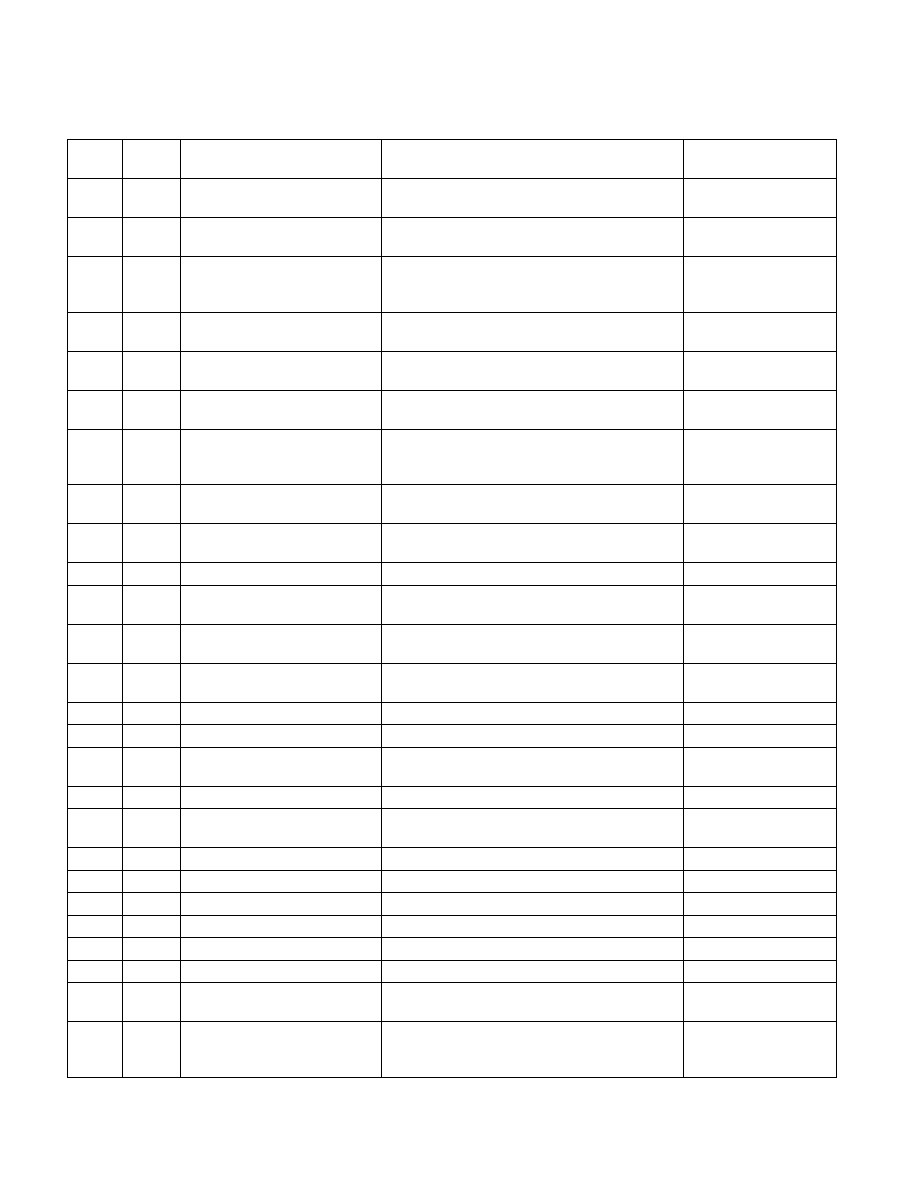

19-40 Vol. 3B

PERFORMANCE-MONITORING EVENTS

C1H

20H

OTHER_ASSISTS.SSE_TO_AVX

Number of transitions from SSE to AVX-256 when

penalty applicable.

C1H

80H

OTHER_ASSISTS.WB

Number of times microcode assist is invoked by

hardware upon uop writeback.

C2H

01H

UOPS_RETIRED.ALL

Counts the number of micro-ops retired, Use

cmask=1 and invert to count active cycles or stalled

cycles.

Supports PEBS, use

Any=1 for core granular.

C2H

02H

UOPS_RETIRED.RETIRE_SLOTS

Counts the number of retirement slots used each

cycle.

Supports PEBS.

C3H

02H

MACHINE_CLEARS.MEMORY_ORD

ERING

Counts the number of machine clears due to

memory order conflicts.

C3H

04H

MACHINE_CLEARS.SMC

Number of self-modifying-code machine clears

detected.

C3H

20H

MACHINE_CLEARS.MASKMOV

Counts the number of executed AVX masked load

operations that refer to an illegal address range

with the mask bits set to 0.

C4H

00H

BR_INST_RETIRED.ALL_BRANCH

ES

Branch instructions at retirement.

See Table 19-1.

C4H

01H

BR_INST_RETIRED.CONDITIONAL Counts the number of conditional branch

instructions retired.

Supports PEBS.

C4H

02H

BR_INST_RETIRED.NEAR_CALL

Direct and indirect near call instructions retired.

Supports PEBS.

C4H

04H

BR_INST_RETIRED.ALL_BRANCH

ES

Counts the number of branch instructions retired.

Supports PEBS.

C4H

08H

BR_INST_RETIRED.NEAR_RETUR

N

Counts the number of near return instructions

retired.

Supports PEBS.

C4H

10H

BR_INST_RETIRED.NOT_TAKEN

Counts the number of not taken branch instructions

retired.

Supports PEBS.

C4H

20H

BR_INST_RETIRED.NEAR_TAKEN Number of near taken branches retired.

Supports PEBS.

C4H

40H

BR_INST_RETIRED.FAR_BRANCH Number of far branches retired.

Supports PEBS.

C5H

00H

BR_MISP_RETIRED.ALL_BRANCH

ES

Mispredicted branch instructions at retirement.

See Table 19-1.

C5H

01H

BR_MISP_RETIRED.CONDITIONAL Mispredicted conditional branch instructions retired. Supports PEBS.

C5H

04H

BR_MISP_RETIRED.ALL_BRANCH

ES

Mispredicted macro branch instructions retired.

Supports PEBS.

C5H

20H

BR_MISP_RETIRED.NEAR_TAKEN Mispredicted taken branch instructions retired.

Supports PEBS.

CAH

02H

FP_ASSIST.X87_OUTPUT

Number of X87 FP assists due to output values.

Supports PEBS.

CAH

04H

FP_ASSIST.X87_INPUT

Number of X87 FP assists due to input values.

Supports PEBS.

CAH

08H

FP_ASSIST.SIMD_OUTPUT

Number of SIMD FP assists due to output values.

Supports PEBS.

CAH

10H

FP_ASSIST.SIMD_INPUT

Number of SIMD FP assists due to input values.

CAH

1EH

FP_ASSIST.ANY

Cycles with any input/output SSE* or FP assists.

CCH

20H

ROB_MISC_EVENTS.LBR_INSERT

S

Count cases of saving new LBR records by

hardware.

CDH

01H

MEM_TRANS_RETIRED.LOAD_LA

TENCY

Randomly sampled loads whose latency is above a

user defined threshold. A small fraction of the

overall loads are sampled due to randomization.

Specify threshold in MSR

3F6H. PMC 3 only.

Table 19-11. Non-Architectural Performance Events In the Processor Core of

3rd Generation Intel® Core™ i7, i5, i3 Processors (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment