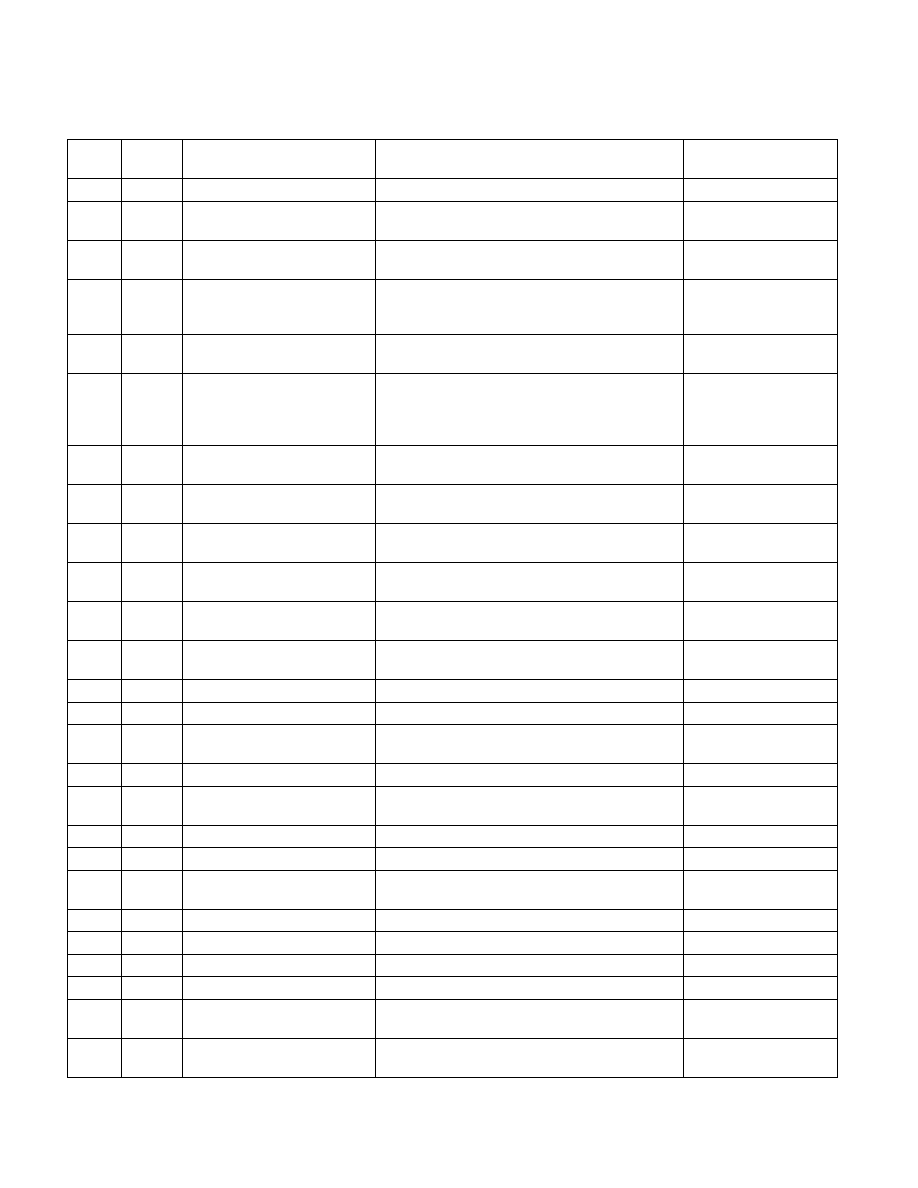

19-22 Vol. 3B

PERFORMANCE-MONITORING EVENTS

08H

60H

DTLB_LOAD_MISSES.STLB_HIT

Number of cache load STLB hits. No page walk.

08H

80H

DTLB_LOAD_MISSES.PDE_CACH

E_MISS

DTLB demand load misses with low part of linear-to-

physical address translation missed.

0DH

03H

INT_MISC.RECOVERY_CYCLES

Cycles waiting to recover after Machine Clears

except JEClear. Set Cmask= 1.

Set Edge to count

occurrences.

0EH

01H

UOPS_ISSUED.ANY

Increments each cycle the # of uops issued by the

RAT to RS. Set Cmask = 1, Inv = 1, Any= 1 to count

stalled cycles of this core.

Set Cmask = 1, Inv = 1to

count stalled cycles.

0EH

10H

UOPS_ISSUED.FLAGS_MERGE

Number of flags-merge uops allocated. Such uops

add delay.

0EH

20H

UOPS_ISSUED.SLOW_LEA

Number of slow LEA or similar uops allocated. Such

uop has 3 sources (for example, 2 sources +

immediate) regardless of whether it is a result of

LEA instruction or not.

0EH

40H

UOPS_ISSUED.SiNGLE_MUL

Number of multiply packed/scalar single precision

uops allocated.

24H

21H

L2_RQSTS.DEMAND_DATA_RD_

MISS

Demand data read requests that missed L2, no

rejects.

24H

41H

L2_RQSTS.DEMAND_DATA_RD_

HIT

Demand data read requests that hit L2 cache.

24H

E1H

L2_RQSTS.ALL_DEMAND_DATA

_RD

Counts any demand and L1 HW prefetch data load

requests to L2.

24H

42H

L2_RQSTS.RFO_HIT

Counts the number of store RFO requests that hit

the L2 cache.

24H

22H

L2_RQSTS.RFO_MISS

Counts the number of store RFO requests that miss

the L2 cache.

24H

E2H

L2_RQSTS.ALL_RFO

Counts all L2 store RFO requests.

24H

44H

L2_RQSTS.CODE_RD_HIT

Number of instruction fetches that hit the L2 cache.

24H

24H

L2_RQSTS.CODE_RD_MISS

Number of instruction fetches that missed the L2

cache.

24H

27H

L2_RQSTS.ALL_DEMAND_MISS

Demand requests that miss L2 cache.

24H

E7H

L2_RQSTS.ALL_DEMAND_REFE

RENCES

Demand requests to L2 cache.

24H

E4H

L2_RQSTS.ALL_CODE_RD

Counts all L2 code requests.

24H

50H

L2_RQSTS.L2_PF_HIT

Counts all L2 HW prefetcher requests that hit L2.

24H

30H

L2_RQSTS.L2_PF_MISS

Counts all L2 HW prefetcher requests that missed

L2.

24H

F8H

L2_RQSTS.ALL_PF

Counts all L2 HW prefetcher requests.

24H

3FH

L2_RQSTS.MISS

All requests that missed L2.

24H

FFH

L2_RQSTS.REFERENCES

All requests to L2 cache.

27H

50H

L2_DEMAND_RQSTS.WB_HIT

Not rejected writebacks that hit L2 cache.

2EH

4FH

LONGEST_LAT_CACHE.REFEREN

CE

This event counts requests originating from the core

that reference a cache line in the last level cache.

2EH

41H

LONGEST_LAT_CACHE.MISS

This event counts each cache miss condition for

references to the last level cache.

Table 19-7. Non-Architectural Performance Events in the Processor Core of

4th Generation Intel® Core™ Processors (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment