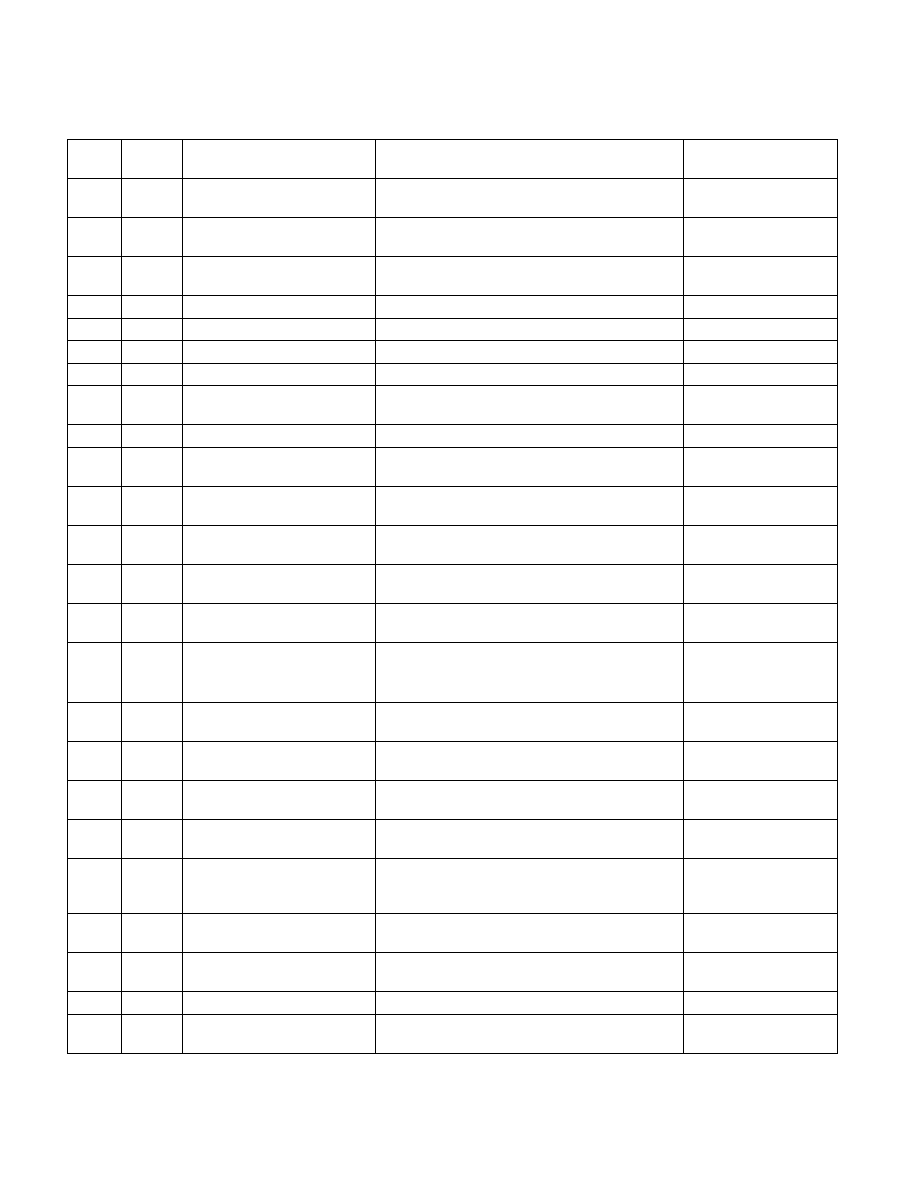

19-18 Vol. 3B

PERFORMANCE-MONITORING EVENTS

BBH

01H

OFF_CORE_RESPONSE_1

See Section 18.9.5, “Off-core Response Performance

Requires MSR 01A7H.

BCH

11H

PAGE_WALKER_LOADS.DTLB_L1 Number of DTLB page walker loads that hit in the

L1+FB.

BCH

21H

PAGE_WALKER_LOADS.ITLB_L1 Number of ITLB page walker loads that hit in the

L1+FB.

BCH

12H

PAGE_WALKER_LOADS.DTLB_L2 Number of DTLB page walker loads that hit in the L2.

BCH

22H

PAGE_WALKER_LOADS.ITLB_L2 Number of ITLB page walker loads that hit in the L2.

BCH

14H

PAGE_WALKER_LOADS.DTLB_L3 Number of DTLB page walker loads that hit in the L3.

BCH

24H

PAGE_WALKER_LOADS.ITLB_L3 Number of ITLB page walker loads that hit in the L3.

BCH

18H

PAGE_WALKER_LOADS.DTLB_M

EMORY

Number of DTLB page walker loads from memory.

C0H

00H

INST_RETIRED.ANY_P

Number of instructions at retirement.

See Table 19-1.

C0H

01H

INST_RETIRED.PREC_DIST

Precise instruction retired event with HW to reduce

effect of PEBS shadow in IP distribution.

PMC1 only.

C0H

02H

INST_RETIRED.X87

FP operations retired. X87 FP operations that have

no exceptions.

C1H

08H

OTHER_ASSISTS.AVX_TO_SSE

Number of transitions from AVX-256 to legacy SSE

when penalty applicable.

C1H

10H

OTHER_ASSISTS.SSE_TO_AVX

Number of transitions from SSE to AVX-256 when

penalty applicable.

C1H

40H

OTHER_ASSISTS.ANY_WB_ASSI

ST

Number of microcode assists invoked by HW upon

uop writeback.

C2H

01H

UOPS_RETIRED.ALL

Counts the number of micro-ops retired.

Use cmask=1 and invert to count active cycles or

stalled cycles.

Supports PEBS and

DataLA, use Any=1 for

core granular.

C2H

02H

UOPS_RETIRED.RETIRE_SLOTS

Counts the number of retirement slots used each

cycle.

Supports PEBS.

C3H

01H

MACHINE_CLEARS.CYCLES

Counts cycles while a machine clears stalled forward

progress of a logical processor or a processor core.

C3H

02H

MACHINE_CLEARS.MEMORY_OR

DERING

Counts the number of machine clears due to memory

order conflicts.

C3H

04H

MACHINE_CLEARS.SMC

Number of self-modifying-code machine clears

detected.

C3H

20H

MACHINE_CLEARS.MASKMOV

Counts the number of executed AVX masked load

operations that refer to an illegal address range with

the mask bits set to 0.

C4H

00H

BR_INST_RETIRED.ALL_BRANC

HES

Branch instructions at retirement.

C4H

01H

BR_INST_RETIRED.CONDITIONA

L

Counts the number of conditional branch instructions

retired.

Supports PEBS.

C4H

02H

BR_INST_RETIRED.NEAR_CALL

Direct and indirect near call instructions retired.

Supports PEBS.

C4H

04H

BR_INST_RETIRED.ALL_BRANC

HES

Counts the number of branch instructions retired.

Supports PEBS.

Table 19-5. Non-Architectural Performance Events of the Processor Core Supported by Broadwell

Microarchitecture (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment