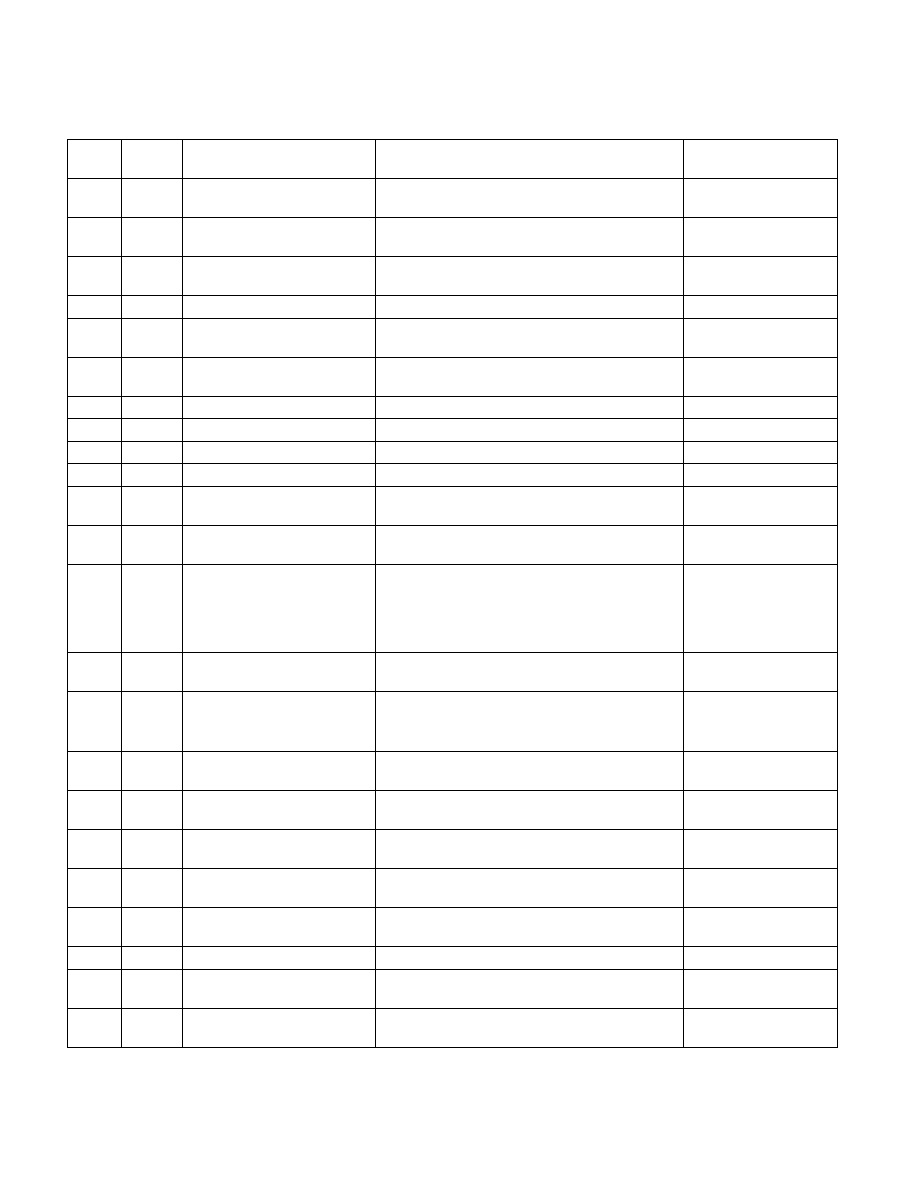

19-14 Vol. 3B

PERFORMANCE-MONITORING EVENTS

14H

01H

ARITH.FPU_DIV_ACTIVE

Cycles when divider is busy executing divide

operations.

24H

21H

L2_RQSTS.DEMAND_DATA_RD_

MISS

Demand data read requests that missed L2, no

rejects.

24H

41H

L2_RQSTS.DEMAND_DATA_RD_

HIT

Demand data read requests that hit L2 cache.

24H

50H

L2_RQSTS.L2_PF_HIT

Counts all L2 HW prefetcher requests that hit L2.

24H

30H

L2_RQSTS.L2_PF_MISS

Counts all L2 HW prefetcher requests that missed

L2.

24H

E1H

L2_RQSTS.ALL_DEMAND_DATA

_RD

Counts any demand and L1 HW prefetch data load

requests to L2.

24H

E2H

L2_RQSTS.ALL_RFO

Counts all L2 store RFO requests.

24H

E4H

L2_RQSTS.ALL_CODE_RD

Counts all L2 code requests.

24H

F8H

L2_RQSTS.ALL_PF

Counts all L2 HW prefetcher requests.

27H

50H

L2_DEMAND_RQSTS.WB_HIT

Not rejected writebacks that hit L2 cache.

2EH

4FH

LONGEST_LAT_CACHE.REFEREN

CE

This event counts requests originating from the core

that reference a cache line in the last level cache.

2EH

41H

LONGEST_LAT_CACHE.MISS

This event counts each cache miss condition for

references to the last level cache.

3CH

00H

CPU_CLK_UNHALTED.THREAD_

P

Counts the number of thread cycles while the thread

is not in a halt state. The thread enters the halt state

when it is running the HLT instruction. The core

frequency may change from time to time due to

power or thermal throttling.

3CH

01H

CPU_CLK_THREAD_UNHALTED.

REF_XCLK

Increments at the frequency of XCLK (100 MHz)

when not halted.

48H

01H

L1D_PEND_MISS.PENDING

Increments the number of outstanding L1D misses

every cycle. Set Cmask = 1 and Edge =1 to count

occurrences.

Counter 2 only.

Set Cmask = 1 to count

cycles.

49H

01H

DTLB_STORE_MISSES.MISS_CAU

SES_A_WALK

Miss in all TLB levels causes a page walk of any page

size (4K/2M/4M/1G).

49H

02H

DTLB_STORE_MISSES.WALK_CO

MPLETED_4K

Completed page walks due to store misses in one or

more TLB levels of 4K page structure.

49H

10H

DTLB_STORE_MISSES.WALK_DU

RATION

Cycles PMH is busy with this walk.

49H

20H

DTLB_STORE_MISSES.STLB_HIT

_4K

Store misses that missed DTLB but hit STLB (4K).

4CH

02H

LOAD_HIT_PRE.HW_PF

Non-SW-prefetch load dispatches that hit fill buffer

allocated for H/W prefetch.

4FH

10H

EPT.WALK_CYCLES

Cycles of Extended Page Table walks.

51H

01H

L1D.REPLACEMENT

Counts the number of lines brought into the L1 data

cache.

58H

04H

MOVE_ELIMINATION.INT_NOT_E

LIMINATED

Number of integer move elimination candidate uops

that were not eliminated.

Table 19-5. Non-Architectural Performance Events of the Processor Core Supported by Broadwell

Microarchitecture (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment