19-10 Vol. 3B

PERFORMANCE-MONITORING EVENTS

C1H

3FH

OTHER_ASSISTS.ANY

Number of times a microcode assist is invoked by HW

other than FP-assist. Examples include AD (page Access

Dirty) and AVX* related assists.

C2H

01H

UOPS_RETIRED.STALL_CYCLES

Cycles without actually retired uops.

CMSK1, INV

C2H

01H

UOPS_RETIRED.TOTAL_CYCLES

Cycles with less than 10 actually retired uops.

CMSK10, INV

C2H

02H

UOPS_RETIRED.RETIRE_SLOTS

Retirement slots used.

C3H

01H

MACHINE_CLEARS.COUNT

Number of machine clears of any type.

CMSK1, EDG

C3H

02H

MACHINE_CLEARS.MEMORY_OR

DERING

Counts the number of machine clears due to memory

order conflicts.

C3H

04H

MACHINE_CLEARS.SMC

Number of self-modifying-code machine clears

detected.

C4H

00H

BR_INST_RETIRED.ALL_BRANC

HES

Branch instructions that retired.

See Table 19-1.

C4H

01H

BR_INST_RETIRED.CONDITIONA

L

Counts the number of conditional branch instructions

retired.

PS

C4H

02H

BR_INST_RETIRED.NEAR_CALL

Direct and indirect near call instructions retired.

PS

C4H

04H

BR_INST_RETIRED.ALL_BRANC

HES

Counts the number of branch instructions retired.

PS

C4H

08H

BR_INST_RETIRED.NEAR_RETU

RN

Counts the number of near return instructions retired.

PS

C4H

10H

BR_INST_RETIRED.NOT_TAKEN Counts the number of not taken branch instructions

retired.

C4H

20H

BR_INST_RETIRED.NEAR_TAKE

N

Number of near taken branches retired.

PS

C4H

40H

BR_INST_RETIRED.FAR_BRANC

H

Number of far branches retired.

PS

C5H

00H

BR_MISP_RETIRED.ALL_BRANC

HES

Mispredicted branch instructions at retirement.

See Table 19-1.

C5H

01H

BR_MISP_RETIRED.CONDITIONA

L

Mispredicted conditional branch instructions retired.

PS

C5H

04H

BR_MISP_RETIRED.ALL_BRANC

HES

Mispredicted macro branch instructions retired.

PS

C5H

20H

BR_MISP_RETIRED.NEAR_TAKE

N

Number of near branch instructions retired that were

mispredicted and taken.

PS

C6H

01H

FRONTEND_RETIRED.DSB_MISS Retired instructions which experienced DSB miss.

Specify MSR_PEBS_FRONTEND.EVTSEL=11H.

PS

C6H

01H

FRONTEND_RETIRED.L1I_MISS

Retired instructions which experienced instruction L1

cache true miss. Specify

MSR_PEBS_FRONTEND.EVTSEL=12H.

PS

C6H

01H

FRONTEND_RETIRED.L2_MISS

Retired instructions which experienced L2 cache true

miss. Specify MSR_PEBS_FRONTEND.EVTSEL=13H.

PS

C6H

01H

FRONTEND_RETIRED.ITLB_MISS Retired instructions which experienced ITLB true miss.

Specify MSR_PEBS_FRONTEND.EVTSEL=14H.

PS

C6H

01H

FRONTEND_RETIRED.STLB_MIS

S

Retired instructions which experienced STLB true miss.

Specify MSR_PEBS_FRONTEND.EVTSEL=15H.

PS

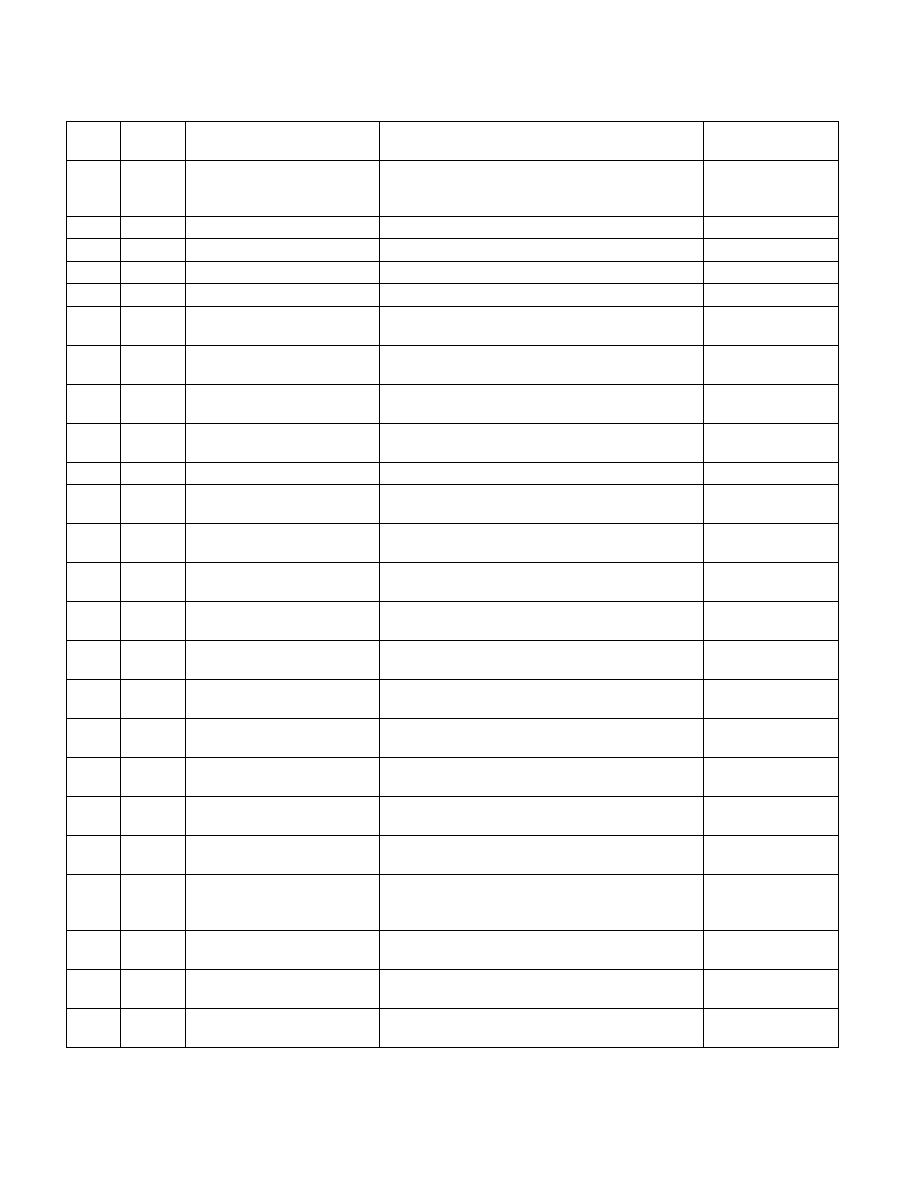

Table 19-3. Non-Architectural Performance Events of the Processor Core Supported by Skylake Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment