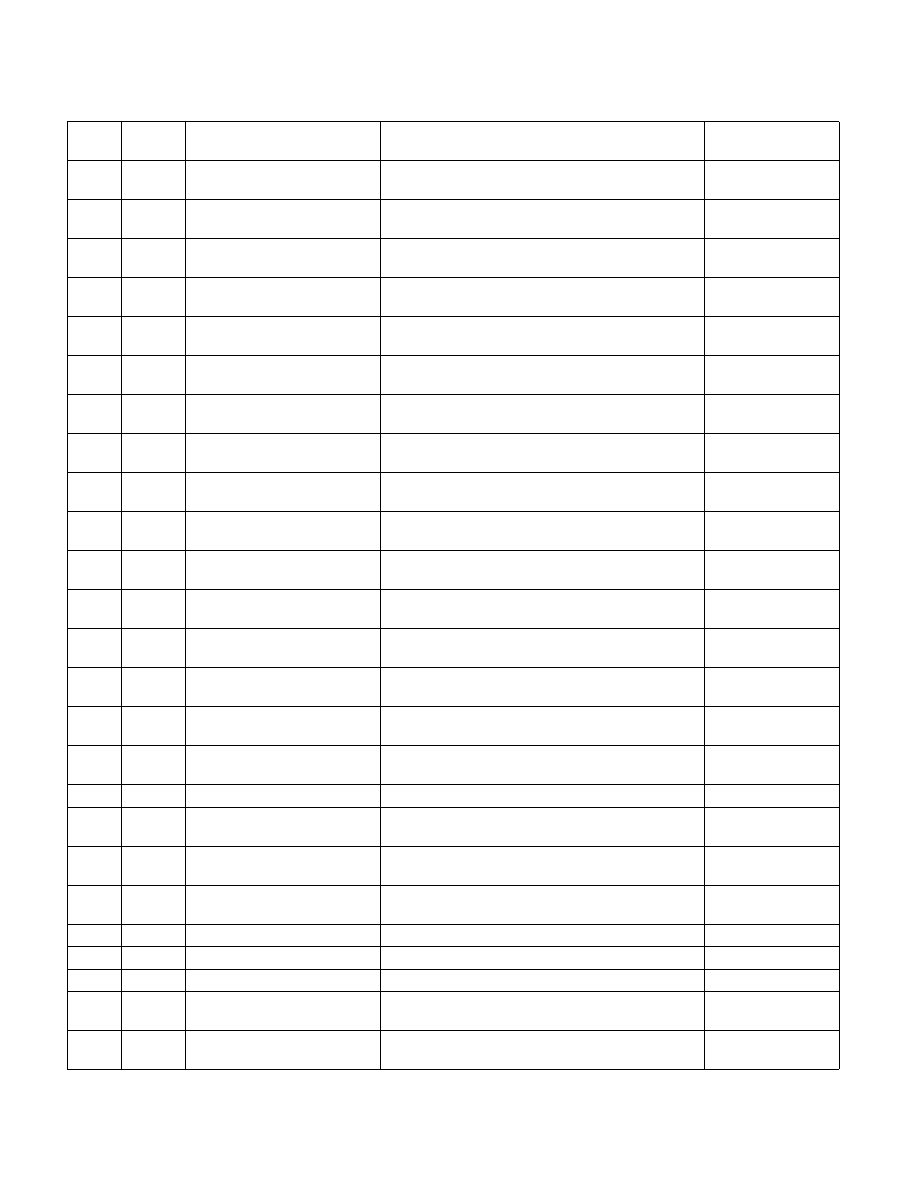

Vol. 3B 19-9

PERFORMANCE-MONITORING EVENTS

B0H

04H

OFFCORE_REQUESTS.DEMAND_

RFO

Demand RFO read requests sent to uncore, including

regular RFOs, locks, ItoM.

B0H

08H

OFFCORE_REQUESTS.ALL_DATA

_RD

Data read requests sent to uncore (demand and

prefetch).

B0H

10H

OFFCORE_REQUESTS.L3_MISS_

DEMAND_DATA_RD

Demand data read requests that missed L3.

B0H

80H

OFFCORE_REQUESTS.ALL_REQU

ESTS

Any memory transaction that reached the SQ.

B1H

01H

UOPS_EXECUTED.THREAD

Counts the number of uops that begin execution across

all ports.

B1H

01H

UOPS_EXECUTED.STALL_CYCLE

S

Cycles where there were no uops that began execution. CMSK, INV

B1H

01H

UOPS_EXECUTED.CYCLES_GE_1

_UOP_EXEC

Cycles where there was at least one uop that began

execution.

CMSK1

B1H

01H

UOPS_EXECUTED.CYCLES_GE_2

_UOP_EXEC

Cycles where there were at least two uops that began

execution.

CMSK2

B1H

01H

UOPS_EXECUTED.CYCLES_GE_3

_UOP_EXEC

Cycles where there were at least three uops that began

execution.

CMSK3

B1H

01H

UOPS_EXECUTED.CYCLES_GE_4

_UOP_EXEC

Cycles where there were at least four uops that began

execution.

CMSK4

B1H

02H

UOPS_EXECUTED.CORE

Counts the number of uops from any logical processor

in this core that begin execution.

B1H

02H

UOPS_EXECUTED.CORE_CYCLES

_GE_1

Cycles where there was at least one uop, from any

logical processor in this core, that began execution.

CMSK1

B1H

02H

UOPS_EXECUTED.CORE_CYCLES

_GE_2

Cycles where there were at least two uops, from any

logical processor in this core, that began execution.

CMSK2

B1H

02H

UOPS_EXECUTED.CORE_CYCLES

_GE_3

Cycles where there were at least three uops, from any

logical processor in this core, that began execution.

CMSK3

B1H

02H

UOPS_EXECUTED.CORE_CYCLES

_GE_4

Cycles where there were at least four uops, from any

logical processor in this core, that began execution.

CMSK4

B1H

02H

UOPS_EXECUTED.CORE_CYCLES

_NONE

Cycles where there were no uops from any logical

processor in this core that began execution.

CMSK1, INV

B1H

10H

UOPS_EXECUTED.X87

Counts the number of X87 uops that begin execution.

B2H

01H

OFF_CORE_REQUEST_BUFFER.S

Q_FULL

Offcore requests buffer cannot take more entries for

this core.

B7H

01H

OFF_CORE_RESPONSE_0

See Section 18.9.5, “Off-core Response Performance

Requires MSR 01A6H

BBH

01H

OFF_CORE_RESPONSE_1

See Section 18.9.5, “Off-core Response Performance

Requires MSR 01A7H

BDH

01H

TLB_FLUSH.DTLB_THREAD

DTLB flush attempts of the thread-specific entries.

BDH

01H

TLB_FLUSH.STLB_ANY

STLB flush attempts.

C0H

00H

INST_RETIRED.ANY_P

Number of instructions at retirement.

C0H

01H

INST_RETIRED.PREC_DIST

Precise instruction retired event with HW to reduce

effect of PEBS shadow in IP distribution.

PMC1 only;

C0H

01H

INST_RETIRED.TOTAL_CYCLES

Number of cycles using always true condition applied to

PEBS instructions retired event.

CMSK10, PS

Table 19-3. Non-Architectural Performance Events of the Processor Core Supported by Skylake Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment