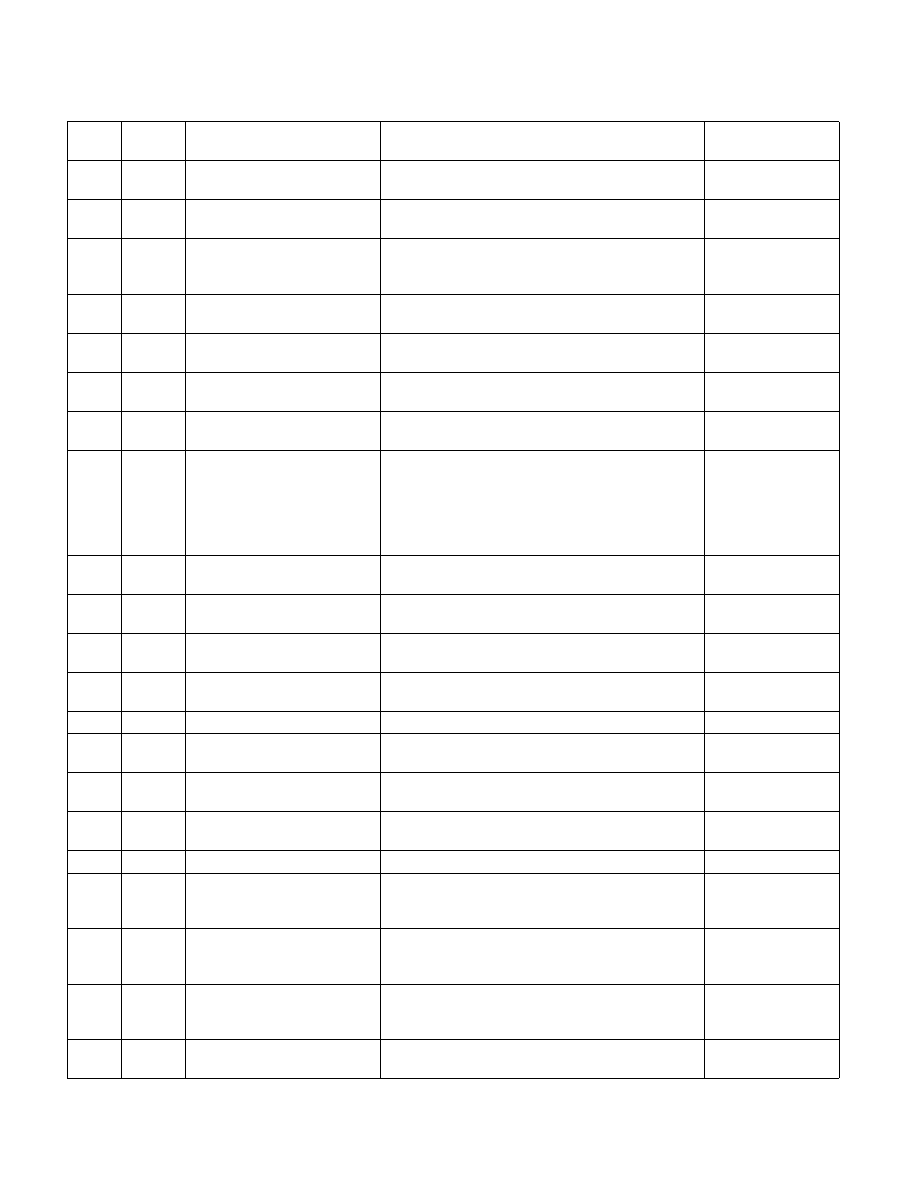

Vol. 3B 19-5

PERFORMANCE-MONITORING EVENTS

3CH

00H

CPU_CLK_UNHALTED.THREAD_

P_ANY

Cycles while at least one logical processor is not in a

halt state.

AnyT

3CH

01H

CPU_CLK_THREAD_UNHALTED.

REF_XCLK

Reference cycles when the logical processor is unhalted

(counts at 100 MHz rate).

3CH

01H

CPU_CLK_THREAD_UNHALTED.

REF_XCLK_ANY

Reference cycles when at least one logical processor in

the processor core is unhalted (counts at 100 MHz

rate).

AnyT

3CH

02H

CPU_CLK_THREAD_UNHALTED.

ONE_THREAD_ACTIVE

Count XClk pulses when this thread is unhalted and the

other thread is halted.

48H

01H

L1D_PEND_MISS.PENDING

Increments the number of outstanding L1D misses

every cycle.

48H

01H

L1D_PEND_MISS.PENDING_CYCL

ES

Cycles with at least one outstanding L1D misses from

this logical processor.

CMSK1

48H

01H

L1D_PEND_MISS.PENDING_CYCL

ES_ANY

Cycles with at least one outstanding L1D misses from

any logical processor in this core.

CMSK1, AnyT

48H

02H

L1D_PEND_MISS.FB_FULL

Number of times a request needed a FB entry but there

was no entry available for it. That is, the FB

unavailability was the dominant reason for blocking the

request. A request includes cacheable/uncacheable

demand that is load, store or SW prefetch. HWP are

excluded.

49H

01H

DTLB_STORE_MISSES.MISS_CAU

SES_A_WALK

Store misses in all TLB levels that cause page walks.

49H

0EH

DTLB_STORE_MISSES.WALK_CO

MPLETED

Counts completed page walks in any TLB levels due to

store misses (all page sizes).

49H

10H

DTLB_STORE_MISSES.WALK_PE

NDING

Counts 1 per cycle for each PMH that is busy with a

page walk for a store.

49H

10H

DTLB_STORE_MISSES.WALK_AC

TIVE

Cycles when at least one PMH is busy with a page walk

for a store.

CMSK1

49H

20H

DTLB_STORE_MISSES.STLB_HIT Store misses that missed DTLB but hit STLB.

4CH

01H

LOAD_HIT_PRE.HW_PF

Demand load dispatches that hit fill buffer allocated for

software prefetch.

4FH

10H

EPT.WALK_PENDING

Counts 1 per cycle for each PMH that is busy with an

EPT walk for any request type.

51H

01H

L1D.REPLACEMENT

Counts the number of lines brought into the L1 data

cache.

5EH

01H

RS_EVENTS.EMPTY_CYCLES

Cycles the RS is empty for the thread.

5EH

01H

RS_EVENTS.EMPTY_END

Counts end of periods where the Reservation Station

(RS) was empty. Could be useful to precisely locate

Front-end Latency Bound issues.

CMSK1, INV

60H

01H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_DATA_RD

Increment each cycle of the number of offcore

outstanding Demand Data Read transactions in SQ to

uncore.

60H

01H

OFFCORE_REQUESTS_OUTSTAN

DING.CYCLES_WITH_DEMAND_D

ATA_RD

Cycles with at least one offcore outstanding Demand

Data Read transactions in SQ to uncore.

CMSK1

60H

01H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_DATA_RD_GE_6

Cycles with at least 6 offcore outstanding Demand Data

Read transactions in SQ to uncore.

CMSK6

Table 19-3. Non-Architectural Performance Events of the Processor Core Supported by Skylake Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment