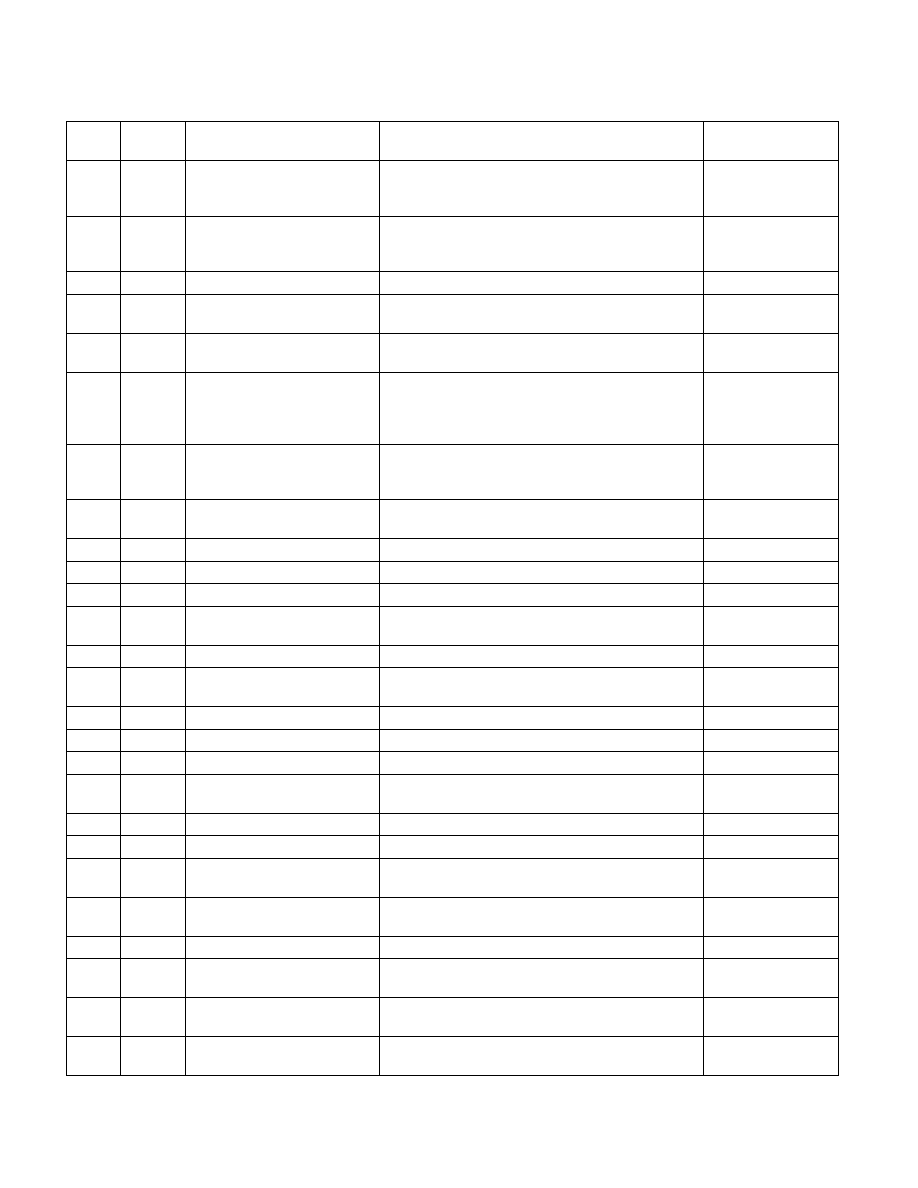

19-4 Vol. 3B

PERFORMANCE-MONITORING EVENTS

0DH

01H

INT_MISC.RECOVERY_CYCLES_A

NY

Core cycles the allocator was stalled due to recovery

from earlier machine clear event for any logical thread

in this processor core.

AnyT

0DH

80H

INT_MISC.CLEAR_RESTEER_CYC

LES

Cycles the issue-stage is waiting for front end to fetch

from resteered path following branch misprediction or

machine clear events.

0EH

01H

UOPS_ISSUED.ANY

The number of uops issued by the RAT to RS.

0EH

01H

UOPS_ISSUED.STALL_CYCLES

Cycles when the RAT does not issue uops to RS for the

thread.

CMSK1, INV

0EH

02H

UOPS_ISSUED.VECTOR_WIDTH_

MISMATCH

Uops inserted at issue-stage in order to preserve upper

bits of vector registers.

0EH

20H

UOPS_ISSUED.SLOW_LEA

Number of slow LEA or similar uops allocated. Such uop

has 3 sources (for example, 2 sources + immediate)

regardless of whether it is a result of LEA instruction or

not.

14H

01H

ARITH.FPU_DIVIDER_ACTIVE

Cycles when divider is busy executing divide or square

root operations. Accounts for FP operations including

integer divides.

24H

21H

L2_RQSTS.DEMAND_DATA_RD_

MISS

Demand Data Read requests that missed L2, no rejects.

24H

22H

L2_RQSTS.RFO_MISS

RFO requests that missed L2.

24H

24H

L2_RQSTS.CODE_RD_MISS

L2 cache misses when fetching instructions.

24H

27H

L2_RQSTS.ALL_DEMAND_MISS

Demand requests that missed L2.

24H

38H

L2_RQSTS.PF_MISS

Requests from the L1/L2/L3 hardware prefetchers or

load software prefetches that miss L2 cache.

24H

3FH

L2_RQSTS.MISS

All requests that missed L2.

24H

41H

L2_RQSTS.DEMAND_DATA_RD_

HIT

Demand Data Read requests that hit L2 cache.

24H

42H

L2_RQSTS.RFO_HIT

RFO requests that hit L2 cache.

24H

44H

L2_RQSTS.CODE_RD_HIT

L2 cache hits when fetching instructions.

24H

D8H

L2_RQSTS.PF_HIT

Prefetches that hit L2.

24H

E1H

L2_RQSTS.ALL_DEMAND_DATA

_RD

All demand data read requests to L2.

24H

E2H

L2_RQSTS.ALL_RFO

All L RFO requests to L2.

24H

E4H

L2_RQSTS.ALL_CODE_RD

All L2 code requests.

24H

E7H

L2_RQSTS.ALL_DEMAND_REFE

RENCES

All demand requests to L2.

24H

F8H

L2_RQSTS.ALL_PF

All requests from the L1/L2/L3 hardware prefetchers

or load software prefetches.

24H

EFH

L2_RQSTS.REFERENCES

All requests to L2.

2EH

4FH

LONGEST_LAT_CACHE.REFEREN

CE

This event counts requests originating from the core

that reference a cache line in the L3 cache.

2EH

41H

LONGEST_LAT_CACHE.MISS

This event counts each cache miss condition for

references to the L3 cache.

3CH

00H

CPU_CLK_UNHALTED.THREAD_

P

Cycles while the logical processor is not in a halt state. See Table 19-1.

Table 19-3. Non-Architectural Performance Events of the Processor Core Supported by Skylake Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment