18-84 Vol. 3B

PERFORMANCE MONITORING

The types of events that can be counted with these performance monitoring facilities are divided into two classes:

non-retirement events and at-retirement events.

•

Non-retirement events (see Table 19-28) are events that occur any time during instruction execution (such as

bus transactions or cache transactions).

•

At-retirement events (see Table 19-29) are events that are counted at the retirement stage of instruction

execution, which allows finer granularity in counting events and capturing machine state.

The at-retirement counting mechanism includes facilities for tagging μops that have encountered a particular

performance event during instruction execution. Tagging allows events to be sorted between those that

occurred on an execution path that resulted in architectural state being committed at retirement as well as

events that occurred on an execution path where the results were eventually cancelled and never committed to

architectural state (such as, the execution of a mispredicted branch).

The Pentium 4 and Intel Xeon processor performance monitoring facilities support the three usage models

described below. The first two models can be used to count both non-retirement and at-retirement events; the

third model is used to count a subset of at-retirement events:

•

Event counting — A performance counter is configured to count one or more types of events. While the

counter is counting, software reads the counter at selected intervals to determine the number of events that

have been counted between the intervals.

MSR_IQ_COUNTER1

13

30DH

MSR_IQ_CCCR1

36DH

MSR_CRU_ESCR0

MSR_CRU_ESCR2

MSR_CRU_ESCR4

MSR_IQ_ESCR0

1

MSR_RAT_ESCR0

MSR_SSU_ESCR0

MSR_ALF_ESCR0

4

5

6

0

2

3

1

3B8H

3CCH

3E0H

3BAH

3BCH

3BEH

3CAH

MSR_IQ_COUNTER2

14

30EH

MSR_IQ_CCCR2

36EH

MSR_CRU_ESCR1

MSR_CRU_ESCR3

MSR_CRU_ESCR5

MSR_IQ_ESCR1

1

MSR_RAT_ESCR1

MSR_ALF_ESCR1

4

5

6

0

2

1

3B9H

3CDH

3E1H

3BBH

3BDH

3CBH

MSR_IQ_COUNTER3

15

30FH

MSR_IQ_CCCR3

36FH

MSR_CRU_ESCR1

MSR_CRU_ESCR3

MSR_CRU_ESCR5

MSR_IQ_ESCR1

1

MSR_RAT_ESCR1

MSR_ALF_ESCR1

4

5

6

0

2

1

3B9H

3CDH

3E1H

3BBH

3BDH

3CBH

MSR_IQ_COUNTER4

16

310H

MSR_IQ_CCCR4

370H

MSR_CRU_ESCR0

MSR_CRU_ESCR2

MSR_CRU_ESCR4

MSR_IQ_ESCR0

1

MSR_RAT_ESCR0

MSR_SSU_ESCR0

MSR_ALF_ESCR0

4

5

6

0

2

3

1

3B8H

3CCH

3E0H

3BAH

3BCH

3BEH

3CAH

MSR_IQ_COUNTER5

17

311H

MSR_IQ_CCCR5

371H

MSR_CRU_ESCR1

MSR_CRU_ESCR3

MSR_CRU_ESCR5

MSR_IQ_ESCR1

1

MSR_RAT_ESCR1

MSR_ALF_ESCR1

4

5

6

0

2

1

3B9H

3CDH

3E1H

3BBH

3BDH

3CBH

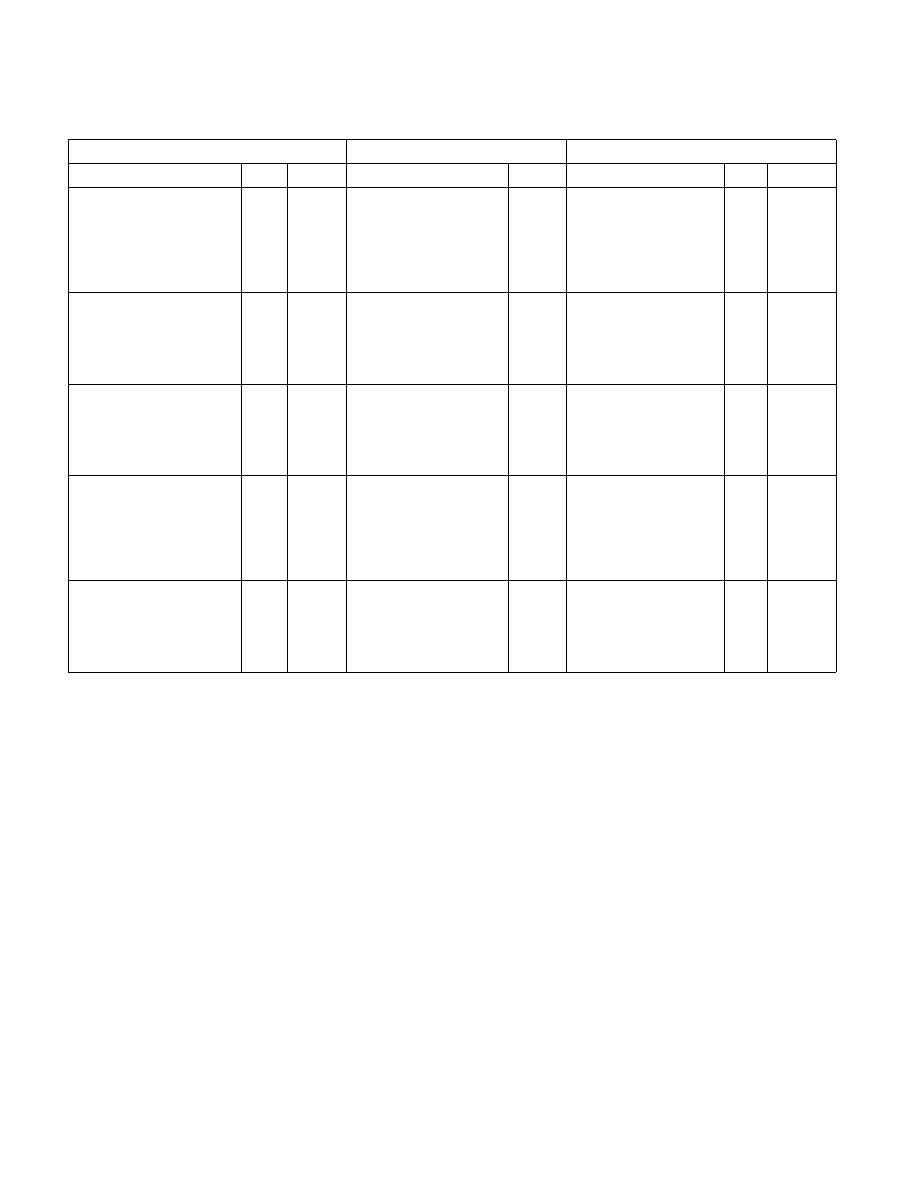

NOTES:

1. MSR_IQ_ESCR0 and MSR_IQ_ESCR1 are available only on early processor builds (family 0FH, models 01H-02H). These MSRs are not

available on later versions.

Table 18-63. Performance Counter MSRs and Associated CCCR and

ESCR MSRs (Processors Based on Intel NetBurst Microarchitecture) (Contd.)

Counter

CCCR

ESCR

Name

No.

Addr

Name

Addr

Name

No.

Addr