Vol. 3B 18-47

PERFORMANCE MONITORING

•

MatchSel (bits 63:61): Software specifies the match criteria according to the following encoding:

— 000B: Disable addr_opcode match hardware

— 100B: Count if only the address field matches,

— 010B: Count if only the opcode field matches

— 110B: Count if either opcode field matches or the address field matches

— 001B: Count only if both opcode and address field match

— Other encoding are reserved

18.8.3 Intel

®

Xeon

®

Processor 7500 Series Performance Monitoring Facility

The performance monitoring facility in the processor core of Intel

®

Xeon

®

processor 7500 series are the same as

those supported in Intel Xeon processor 5500 series. The uncore subsystem in Intel Xeon processor 7500 series

are significantly different The uncore performance monitoring facility consist of many distributed units associated

with individual logic control units (referred to as boxes) within the uncore subsystem. A high level block diagram of

the various box units of the uncore is shown in Figure 18-31.

Uncore PMUs are programmed via MSR interfaces. Each of the distributed uncore PMU units have several general-

purpose counters. Each counter requires an associated event select MSR, and may require additional MSRs to

configure sub-event conditions. The uncore PMU MSRs associated with each box can be categorized based on its

functional scope: per-counter, per-box, or global across the uncore. The number counters available in each box

type are different. Each box generally provides a set of MSRs to enable/disable, check status/overflow of multiple

counters within each box.

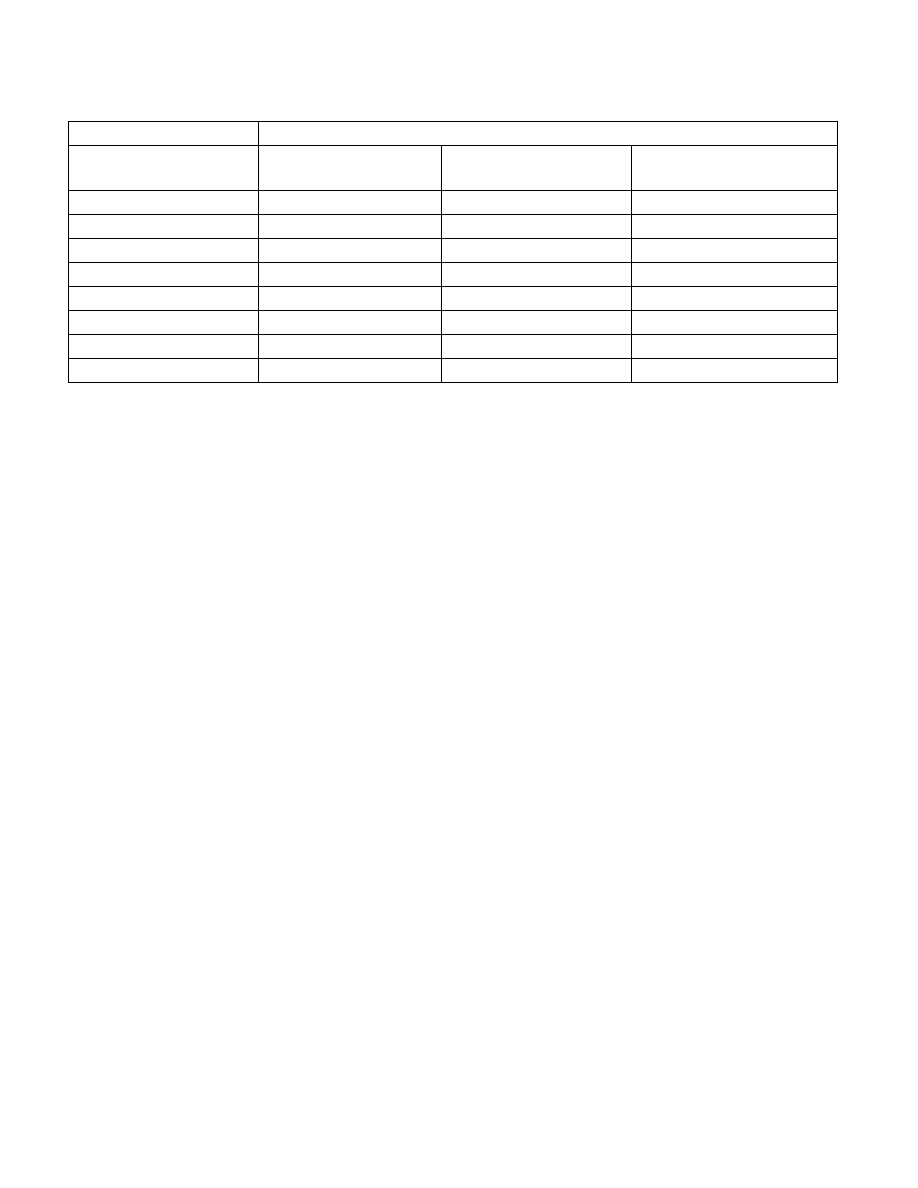

Table 18-27. Opcode Field Encoding for MSR_UNCORE_ADDR_OPCODE_MATCH

Opcode [43:40]

QPI Message Class

Home Request

[47:44] = 0000B

Snoop Response

[47:44] = 0001B

Data Response

[47:44] = 1110B

1

DMND_IFETCH

2

2

WB

3

3

PF_DATA_RD

4

4

PF_RFO

5

5

PF_IFETCH

6

6

OTHER

7

7

NON_DRAM

15

15