18-44 Vol. 3B

PERFORMANCE MONITORING

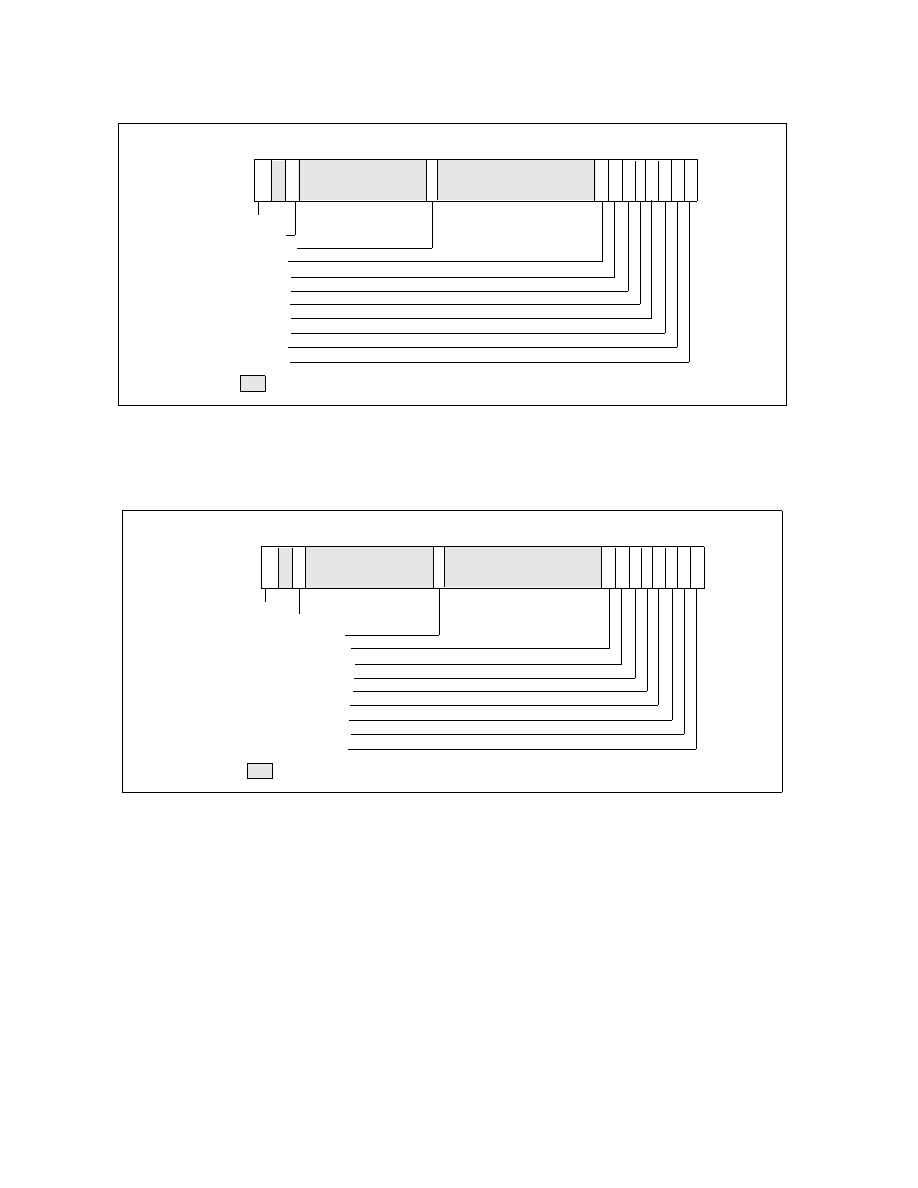

Figure 18-27 shows the layout of MSR_UNCORE_PERF_GLOBAL_OVF_CTRL.

•

CLR_OVF_PCn (bit n, n = 0, 7): Set this bit to clear the overflow status for general-purpose uncore counter

MSR_UNCORE_PerfCntr n. Writing a value other than 1 is ignored.

•

CLR_OVF_FC0 (bit 32): Set this bit to clear the overflow status for the fixed-function uncore counter

MSR_UNCORE_FixedCntr0. Writing a value other than 1 is ignored.

•

CLR_OVF_PMI (bit 61): Set this bit to clear the OVF_PMI flag in MSR_UNCORE_PERF_GLOBAL_STATUS. Writing

a value other than 1 is ignored.

•

CLR_CHG (bit 63): Set this bit to clear the CHG flag in MSR_UNCORE_PERF_GLOBAL_STATUS register. Writing

a value other than 1 is ignored.

Figure 18-26. Layout of MSR_UNCORE_PERF_GLOBAL_STATUS MSR

Figure 18-27. Layout of MSR_UNCORE_PERF_GLOBAL_OVF_CTRL MSR

CHG (R/W)

OVF_PMI (R/W)

8 7

0

32

3

1

Reserved

63

2

4

31

5

6

62

60

61

OVF_PC7 (R/O)

OVF_PC6 (R/O)

OVF_PC5 (R/O)

OVF_PC4 (R/O)

OVF_PC3 (R/O)

OVF_PC2 (R/O)

OVF_PC1 (R/O)

OVF_PC0 (R/O)

OVF_FC0 (R/O)

RESET Value — 00000000_00000000H

CLR_CHG (WO1)

CLR_OVF_PMI (WO1)

8 7

0

32

3

1

Reserved

63

2

4

31

5

6

62

60

61

CLR_OVF_PC7 (WO1)

CLR_OVF_PC6 (WO1)

CLR_OVF_PC5 (WO1)

CLR_OVF_PC4 (WO1)

CLR_OVF_PC3 (WO1)

CLR_OVF_PC2 (WO1)

CLR_OVF_PC1 (WO1)

CLR_OVF_PC0 (WO1)

CLR_OVF_FC0 (WO1)

RESET Value — 00000000_00000000H