Vol. 3B 18-43

PERFORMANCE MONITORING

•

EN_PMI_COREn (bit n, n = 0, 3 if four cores are present): When set, processor core n is programmed to receive

an interrupt signal from any interrupt enabled uncore counter. PMI delivery due to an uncore counter overflow

is enabled by setting IA32_DEBUGCTL.Offcore_PMI_EN to 1.

•

PMI_FRZ (bit 63): When set, all U-clock uncore counters are disabled when any one of them signals a

performance interrupt. Software must explicitly re-enable the counter by setting the enable bits in

MSR_UNCORE_PERF_GLOBAL_CTRL upon exit from the ISR.

MSR_UNCORE_PERF_GLOBAL_STATUS provides overflow status of the U-clock performance counters in the

uncore. This is a read-only register. If an overflow status bit is set the corresponding counter has overflowed. The

register provides a condition change bit (bit 63) which can be quickly checked by software to determine if a signif-

icant change has occurred since the last time the condition change status was cleared. Figure 18-26 shows the

layout of MSR_UNCORE_PERF_GLOBAL_STATUS.

•

OVF_PCn (bit n, n = 0, 7): When set, indicates general-purpose uncore counter MSR_UNCORE_PerfCntr n has

overflowed.

•

OVF_FC0 (bit 32): When set, indicates the fixed-function uncore counter MSR_UNCORE_FixedCntr0 has

overflowed.

•

OVF_PMI (bit 61): When set indicates that an uncore counter overflowed and generated an interrupt request.

•

CHG (bit 63): When set indicates that at least one status bit in MSR_UNCORE_PERF_GLOBAL_STATUS register

has changed state.

MSR_UNCORE_PERF_GLOBAL_OVF_CTRL allows software to clear the status bits in the

UNCORE_PERF_GLOBAL_STATUS register. This is a write-only register, and individual status bits in the global

status register are cleared by writing a binary one to the corresponding bit in this register. Writing zero to any bit

position in this register has no effect on the uncore PMU hardware.

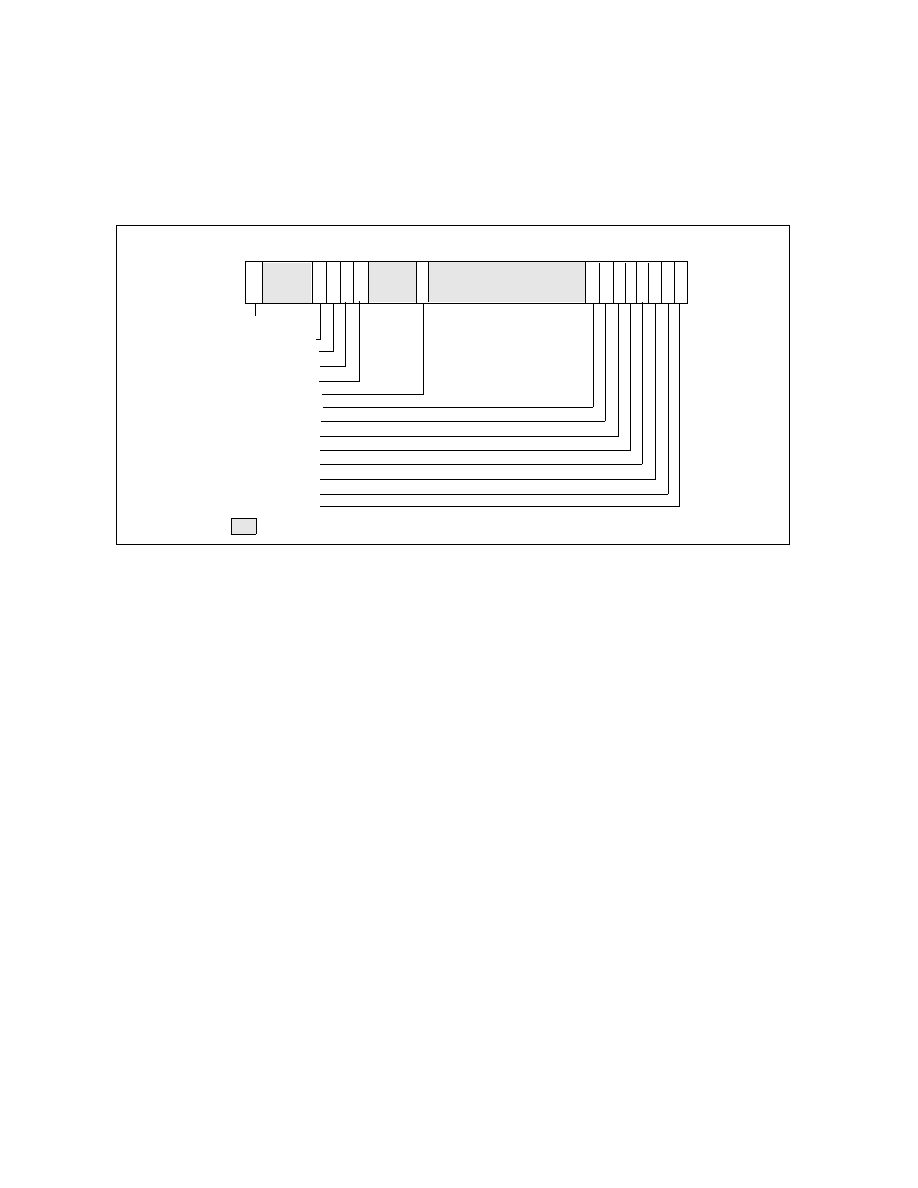

Figure 18-25. Layout of MSR_UNCORE_PERF_GLOBAL_CTRL MSR

PMI_FRZ (R/W)

EN_PMI_CORE3 (R/W)

EN_PMI_CORE2 (R/W)

EN_PMI_CORE1 (R/W)

8 7

0

EN_PMI_CORE0 (R/W)

32

3

48

1

Reserved

63

2

4

31

5

6

62

49

50

51

EN_PC7 (R/W)

EN_PC6 (R/W)

EN_PC5 (R/W)

EN_PC4 (R/W)

EN_PC3 (R/W)

EN_PC2 (R/W)

EN_PC1 (R/W)

EN_PC0 (R/W)

EN_FC0 (R/W)

RESET Value — 00000000_00000000H