18-22 Vol. 3B

PERFORMANCE MONITORING

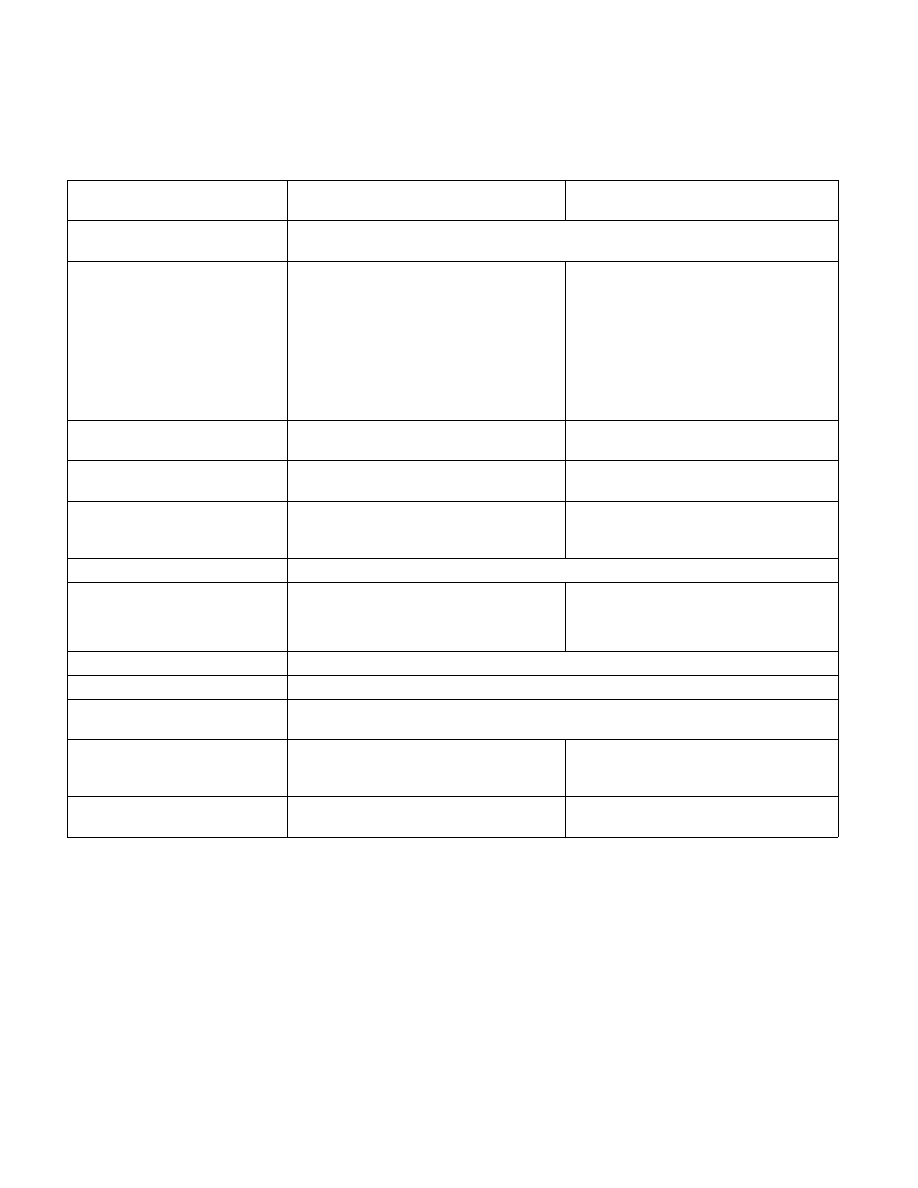

A comparison of the sequence of requirements to program PEBS for processors based on Intel Core and Intel

NetBurst microarchitectures is listed in Table 18-11.

18.4.4.4 Re-configuring PEBS Facilities

When software needs to reconfigure PEBS facilities, it should allow a quiescent period between stopping the prior

event counting and setting up a new PEBS event. The quiescent period is to allow any latent residual PEBS records

to complete its capture at their previously specified buffer address (provided by IA32_DS_AREA).

Table 18-11. Requirements to Program PEBS

For Processors based on Intel Core

microarchitecture

For Processors based on Intel NetBurst

microarchitecture

Verify PEBS support of

processor/OS

• IA32_MISC_ENABLE.EMON_AVAILABE (bit 7) is set.

• IA32_MISC_ENABLE.PEBS_UNAVAILABE (bit 12) is clear.

Ensure counters are in disabled

On initial set up or changing event

configurations, write

MSR_PERF_GLOBAL_CTRL MSR (38FH) with 0.

On subsequent entries:

• Clear all counters if “Counter Freeze on PMI“

is not enabled.

• If IA32_DebugCTL.Freeze is enabled,

counters are automatically disabled.

Counters MUST be stopped before writing.

1

NOTES:

1. Counters read while enabled are not guaranteed to be precise with event counts that occur in timing proximity to the RDMSR.

Optional

Disable PEBS.

Clear ENABLE PMC0 bit in IA32_PEBS_ENABLE

MSR (3F1H).

Optional

Check overflow conditions.

Check MSR_PERF_GLOBAL_STATUS MSR

(38EH) handle any overflow conditions.

Check OVF flag of each CCCR for overflow

condition

Clear overflow status.

Clear MSR_PERF_GLOBAL_STATUS MSR

(38EH) using IA32_PERF_GLOBAL_OVF_CTRL

MSR (390H).

Clear OVF flag of each CCCR.

Write “sample-after“ values.

Configure the counter(s) with the sample after value.

Configure specific counter

configuration MSR.

• Set local enable bit 22 - 1.

• Do NOT set local counter PMI/INT bit, bit 20

- 0.

• Event programmed must be PEBS capable.

• Set appropriate OVF_PMI bits - 1.

• Only CCCR for MSR_IQ_COUNTER4 support

PEBS.

Allocate buffer for PEBS states.

Allocate a buffer in memory for the precise information.

Program the IA32_DS_AREA MSR.

Program the IA32_DS_AREA MSR.

Configure the PEBS buffer

management records.

Configure the PEBS buffer management records in the DS buffer management area.

Configure/Enable PEBS.

Set Enable PMC0 bit in IA32_PEBS_ENABLE

MSR (3F1H).

Configure MSR_PEBS_ENABLE,

MSR_PEBS_MATRIX_VERT and

MSR_PEBS_MATRIX_HORZ as needed.

Enable counters.

Set Enable bits in MSR_PERF_GLOBAL_CTRL

MSR (38FH).

Set each CCCR enable bit 12 - 1.