Vol. 3B 17-59

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

when CDP is enabled. In order to simplify this behavior and prevent unintended remapping software should

consider resetting all threads to COS[0] before enabling or disabling CDP.

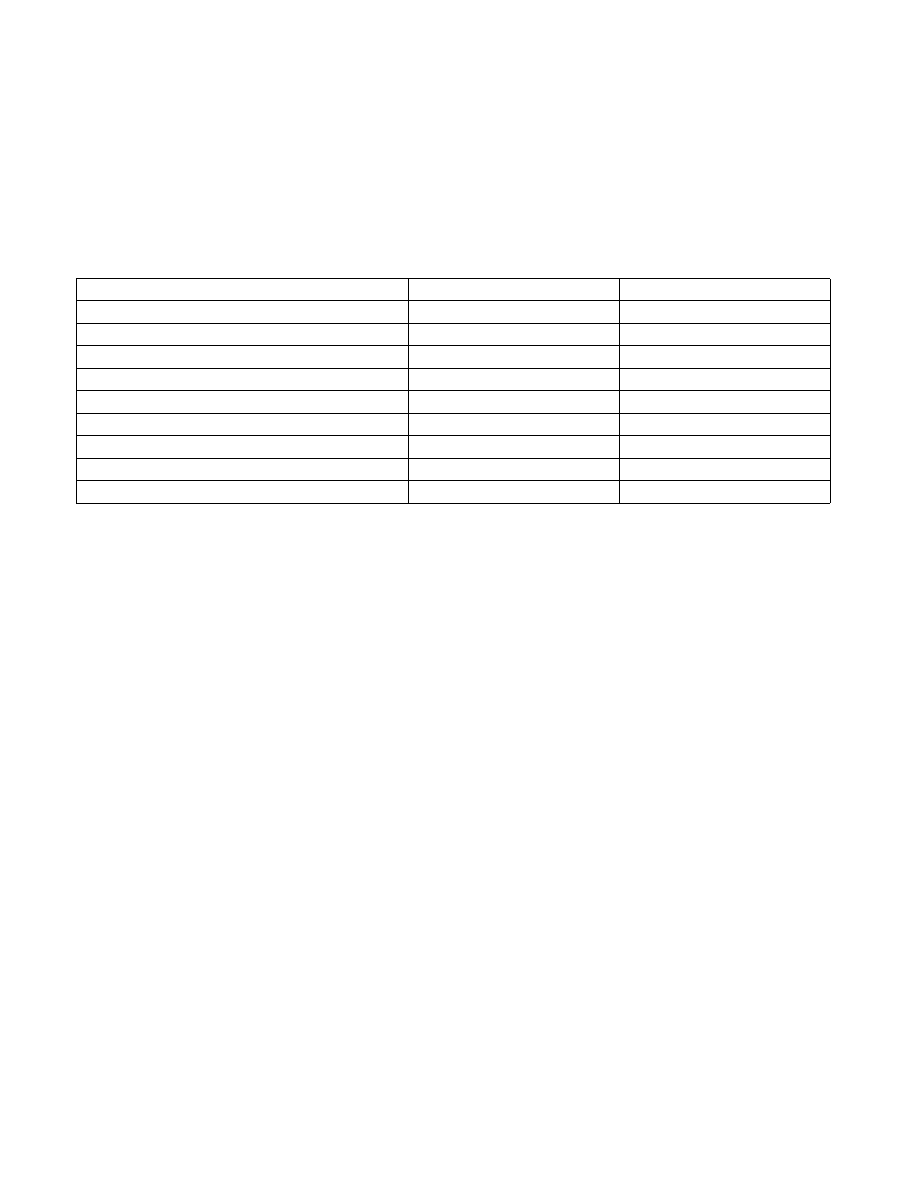

17.17.4.1 Mapping Between L3 CDP Masks and CAT Masks

When CDP is enabled, the existing CAT mask MSR space is re-mapped to provide a code mask and a data mask per

COS. The re-mapping is shown in

Table 17-20. Re-indexing of COS Numbers and Mapping to CAT/CDP Mask MSRs

One can derive the MSR address for the data mask or code mask for a given COS number ‘n’ by:

•

data_mask_address (n) = base + (n <<1), where base is the address of IA32_L3_QOS_MASK_0.

•

code_mask_address (n) = base + (n <<1) +1.

When CDP is enabled, each COS is mapped 1:2 with mask MSRs, with one mask enabling programmatic control

over data fill location and one mask enabling control over data placement. A variety of overlapped and isolated

mask configurations are possible (see the example in Figure 17-29).

Mask MSR field definitions remain the same. Capacity masks must be formed of contiguous set bits, with a length

of 1 bit or longer and should not exceed the maximum mask length specified in CPUID. As examples, valid masks

on a cache with max bitmask length of 16b (from CPUID) include 0xFFFF, 0xFF00, 0x00FF, 0x00F0, 0x0001,

0x0003 and so on. Maximum valid mask lengths are unchanged whether CDP is enabled or disabled, and writes of

invalid mask values may lead to undefined behavior. Writes to reserved bits will generate #GP(0).

17.17.4.2 L3 CAT: Disabling CDP

Before enabling or disabling CDP, software should write all 1's to all of the CAT/CDP masks to ensure proper

behavior (e.g., the IA32_L3_QOS_Mask_n set of MSRs).

Software should also account for the fact that mask interpretations change when CDP is enabled or disabled,

meaning for instance that a CAT mask for a given COS may become a code mask for a different Class of Service

when CDP is enabled. In order to simplify this behavior and prevent unintended remapping software should

consider resetting all threads to COS[0] before enabling or disabling CDP.

17.17.5 Cache Allocation Technology Programming Considerations

17.17.5.1 Cache Allocation Technology Dynamic Configuration

Both the CAT masks and CQM registers are accessible and modifiable at any time during execution using

RDMSR/WRMSR unless otherwise noted. When writing to these MSRs a #GP(0) will be generated if any of the

following conditions occur:

•

A reserved bit is modified,

Mask MSR

CAT-only Operation

CDP Operation

IA32_L3_QOS_Mask_0

COS0

COS0.Data

IA32_L3_QOS_Mask_1

COS1

COS0.Code

IA32_L3_QOS_Mask_2

COS2

COS1.Data

IA32_L3_QOS_Mask_3

COS3

COS1.Code

IA32_L3_QOS_Mask_4

COS4

COS2.Data

IA32_L3_QOS_Mask_5

COS5

COS2.Code

....

....

....

IA32_L3_QOS_Mask_’2n’

COS’2n’

COS’n’.Data

IA32_L3_QOS_Mask_’2n+1’

COS’2n+1’

COS’n’.Code