1-8 Vol. 3A

ABOUT THIS MANUAL

The processor also supports segmented addressing. This is a form of addressing where a program may have many

independent address spaces, called segments. For example, a program can keep its code (instructions) and stack

in separate segments. Code addresses would always refer to the code space, and stack addresses would always

refer to the stack space. The following notation is used to specify a byte address within a segment:

Segment-register:Byte-address

For example, the following segment address identifies the byte at address FF79H in the segment pointed by the DS

register:

DS:FF79H

The following segment address identifies an instruction address in the code segment. The CS register points to the

code segment and the EIP register contains the address of the instruction.

CS:EIP

1.3.6

Syntax for CPUID, CR, and MSR Values

Obtain feature flags, status, and system information by using the CPUID instruction, by checking control register

bits, and by reading model-specific registers. We are moving toward a single syntax to represent this type of infor-

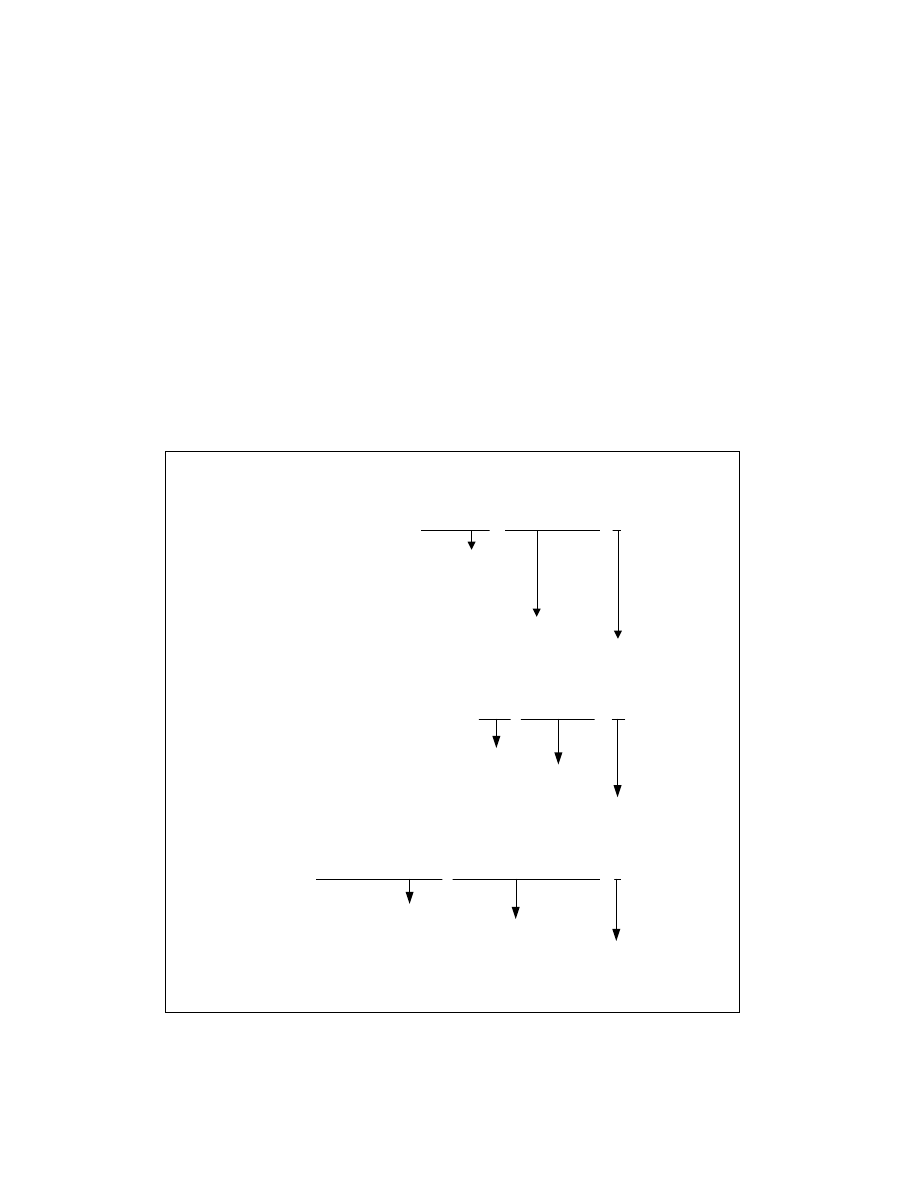

mation. See Figure 1-2.

Figure 1-2. Syntax for CPUID, CR, and MSR Data Presentation

For Control Register Values

For Model-Specific Register Values

CPUID.01H : ECX.SSE [bit 25] = 1

Value (or range) of output

Syntax Representation for CPUID Input and Output

Output register and feature flag or

field name with bit position(s)

CR4.OSFXSR[bit 9] = 1

Feature flag or field name

with bit position(s)

Value (or range) of output

Example CR name

Feature flag or field name with bit position(s)

IA32_MISC_ENABLES.ENABLEFOPCODE[bit 2] = 1

Value (or range) of output

Example MSR name

OM17732

Input value for EAX defines output

(NOTE: Some leaves require input values for

EAX and ECX. If only one value is present,

EAX is implied.)