17-6 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

17.2.6

Debug Registers and Intel

®

64 Processors

For Intel 64 architecture processors, debug registers DR0–DR7 are 64 bits. In 16-bit or 32-bit modes (protected

mode and compatibility mode), writes to a debug register fill the upper 32 bits with zeros. Reads from a debug

register return the lower 32 bits. In 64-bit mode, MOV DRn instructions read or write all 64 bits. Operand-size

prefixes are ignored.

In 64-bit mode, the upper 32 bits of DR6 and DR7 are reserved and must be written with zeros. Writing 1 to any of

the upper 32 bits results in a #GP(0) exception (see Figure 17-2). All 64 bits of DR0–DR3 are writable by software.

However, MOV DRn instructions do not check that addresses written to DR0–DR3 are in the linear-address limits of

the processor implementation (address matching is supported only on valid addresses generated by the processor

implementation). Break point conditions for 8-byte memory read/writes are supported in all modes.

17.3 DEBUG

EXCEPTIONS

The Intel 64 and IA-32 architectures dedicate two interrupt vectors to handling debug exceptions: vector 1 (debug

exception, #DB) and vector 3 (breakpoint exception, #BP). The following sections describe how these exceptions

are generated and typical exception handler operations.

17.3.1

Debug Exception (#DB)—Interrupt Vector 1

The debug-exception handler is usually a debugger program or part of a larger software system. The processor

generates a debug exception for any of several conditions. The debugger checks flags in the DR6 and DR7 registers

to determine which condition caused the exception and which other conditions might apply. Table 17-2 shows the

states of these flags following the generation of each kind of breakpoint condition.

Instruction-breakpoint and general-detect condition (see Section 17.3.1.3, “General-Detect Exception Condition”)

result in faults; other debug-exception conditions result in traps. The debug exception may report one or both at

one time. The following sections describe each class of debug exception.

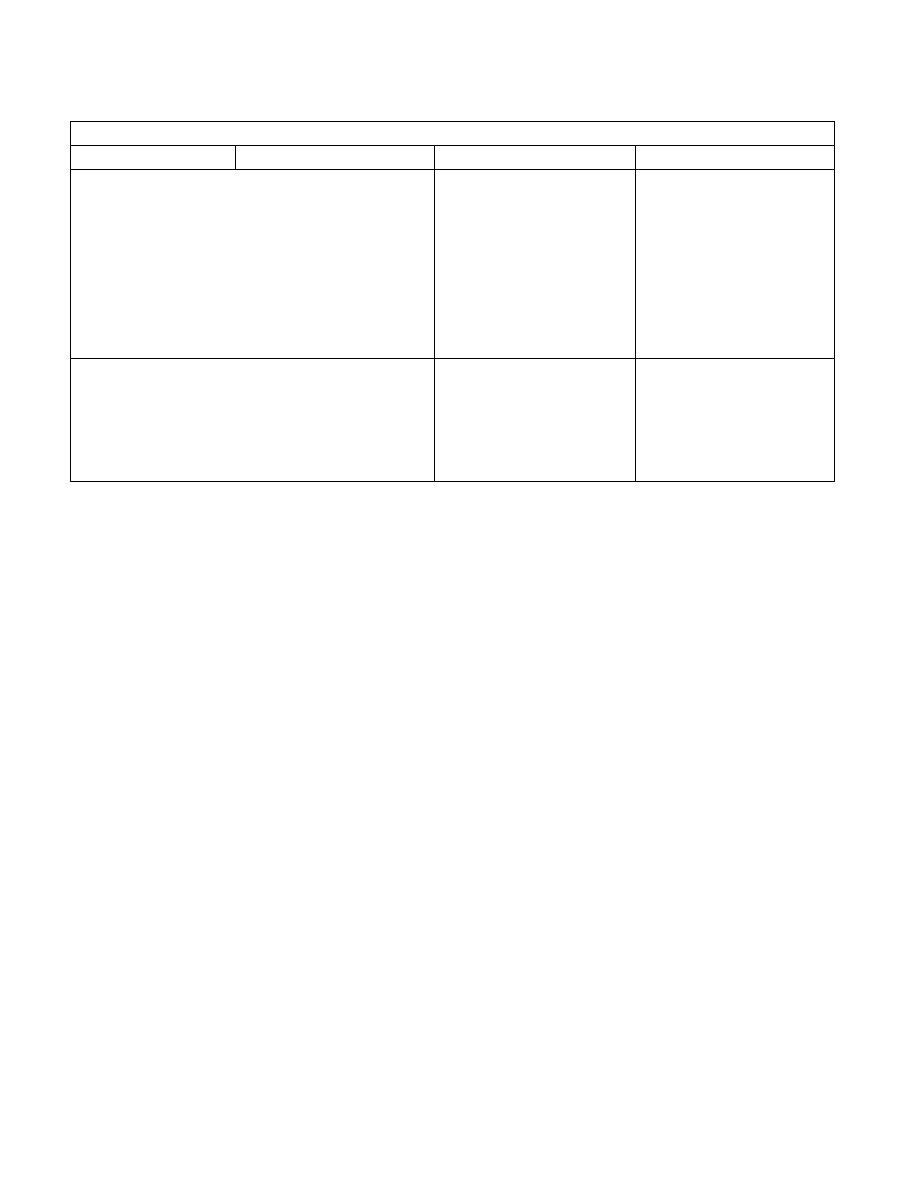

Data operations that trap

- Read or write

- Read or write

- Write

- Write

- Read or write

- Read or write

- Read or write

- Write

- Write

- Write

A0001H

A0001H

A0002H

A0002H

B0001H

B0002H

B0002H

C0000H

C0001H

C0003H

1

2

1

2

4

1

2

4

2

1

Data operations that do not trap

- Read or write

- Read

- Read or write

- Read or write

- Read

- Read or write

A0000H

A0002H

A0003H

B0000H

C0000H

C0004H

1

1

4

2

2

4

Table 17-1. Breakpoint Examples (Contd.)

Debug Register Setup

Debug Register

R/Wn

Breakpoint Address

LENn