16-22 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

16.9

INCREMENTAL DECODING INFORMATION: PROCESSOR FAMILY WITH CPUID

DISPLAYFAMILY_DISPLAYMODEL SIGNATURE 06_55H, MACHINE ERROR

CODES FOR MACHINE CHECK

Future Intel Xeon processors with CPUID DisplayFamily_DisplaySignature 06_55H. Incremental error codes for

internal machine check error from PCU controller is reported in the register bank IA32_MC4, Table 16-27 in Section

16.9.1 lists model-specific fields to interpret error codes applicable to IA32_MC4_STATUS.

16.9.1 Internal Machine Check Errors

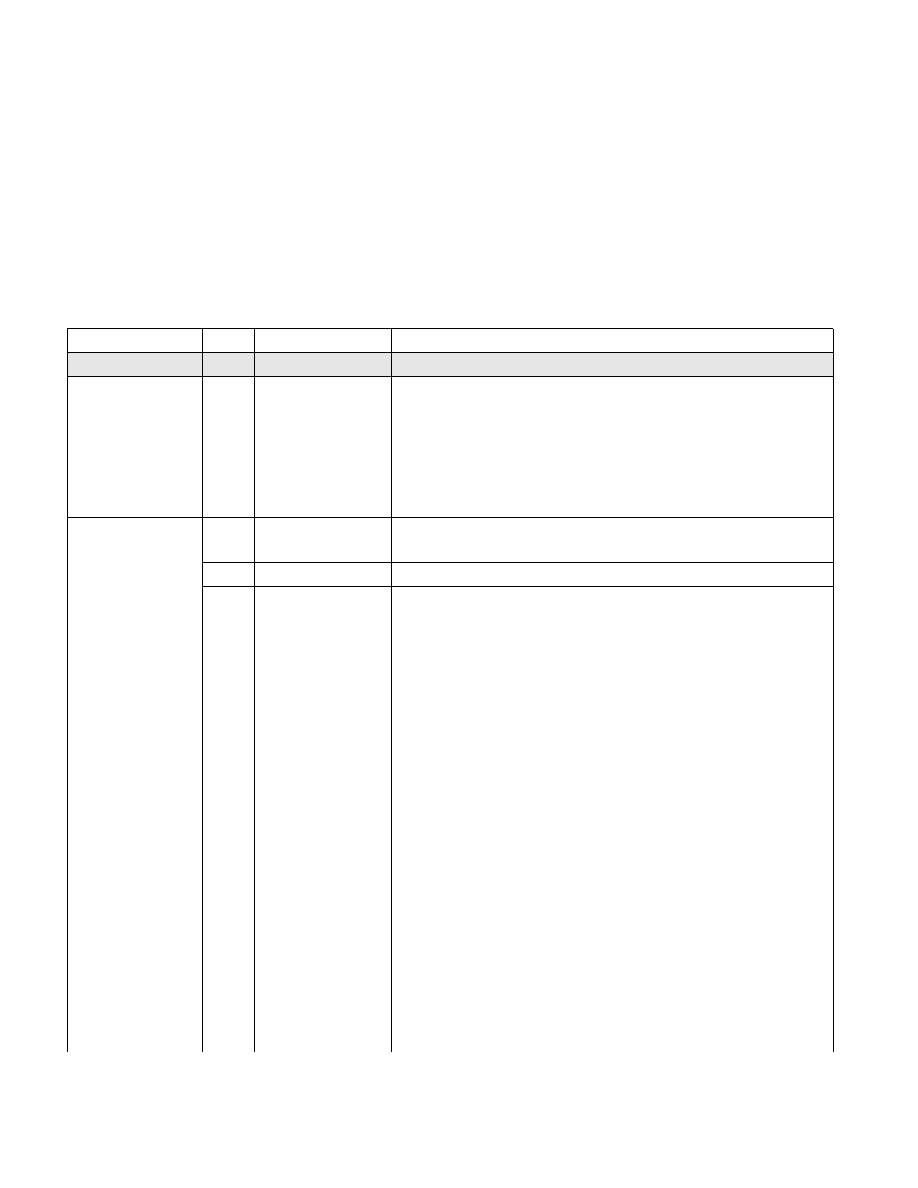

Table 16-27. Machine Check Error Codes for IA32_MC4_STATUS

Type

Bit No. Bit Function

Bit Description

MCA error codes

1

15:0

MCACOD

MCACOD

2

15:0

internal Errors

0402h - PCU internal Errors

0403h - PCU internal Errors

0406h - Intel TXT Errors

0407h - Other UBOX internal Errors.

On an IERR caused by a core 3-strike the IA32_MC3_STATUS (MLC) is copied

to the IA32_MC4_STATUS (After a 3-strike, the core MCA banks will be

unavailable).

Model specific errors 19:16

Reserved except for

the following

0000b - No Error

00xxb - PCU internal error

23-20

Reserved

Reserved

31-24

Reserved except for

the following

00h - No Error

0Dh - MCA_DMI_TRAINING_TIMEOUT

0Fh - MCA_DMI_CPU_RESET_ACK_TIMEOUT

10h - MCA_MORE_THAN_ONE_LT_AGENT

1Eh - MCA_BIOS_RST_CPL_INVALID_SEQ

1Fh - MCA_BIOS_INVALID_PKG_STATE_CONFIG

25h - MCA_MESSAGE_CHANNEL_TIMEOUT

27h - MCA_MSGCH_PMREQ_CMP_TIMEOUT

30h - MCA_PKGC_DIRECT_WAKE_RING_TIMEOUT

31h - MCA_PKGC_INVALID_RSP_PCH

33h - MCA_PKGC_WATCHDOG_HANG_CBZ_DOWN

34h - MCA_PKGC_WATCHDOG_HANG_CBZ_UP

38h - MCA_PKGC_WATCHDOG_HANG_C3_UP_SF

40h - MCA_SVID_VCCIN_VR_ICC_MAX_FAILURE

41h - MCA_SVID_COMMAND_TIMEOUT

42h - MCA_SVID_VCCIN_VR_VOUT_MAX_FAILURE

43h - MCA_SVID_CPU_VR_CAPABILITY_ERROR

44h - MCA_SVID_CRITICAL_VR_FAILED

45h - MCA_SVID_SA_ITD_ERROR

46h - MCA_SVID_READ_REG_FAILED

47h - MCA_SVID_WRITE_REG_FAILED

48h - MCA_SVID_PKGC_INIT_FAILED