16-6 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

16.2.1.1 Processor Machine Check Status Register

Incremental MCA Error Code Definition

Intel Xeon processor 7400 series use compound MCA Error Codes for logging its Bus internal machine check

errors, L3 Errors, and Bus/Interconnect Errors. It defines incremental Machine Check error types

(IA32_MC6_STATUS[15:0]) beyond those defined in Chapter 15. Table 16-5 lists these incremental MCA error

code types that apply to IA32_MC6_STATUS. Error code details are specified in MC6_STATUS [31:16] (see

Section 16.2.2), the “Model Specific Error Code” field. The information in the “Other_Info” field

(MC4_STATUS[56:32]) is common to the three processor error types and contains a correctable event count and

specifies the MC6_MISC register format.

The Bold faced binary encodings are the only encodings used by the processor for MC4_STATUS[15:0].

16.2.2 Intel Xeon Processor 7400 Model Specific Error Code Field

16.2.2.1 Processor Model Specific Error Code Field

Type B: Bus and Interconnect Error

Note:

The Model Specific Error Code field in MC6_STATUS (bits 31:16).

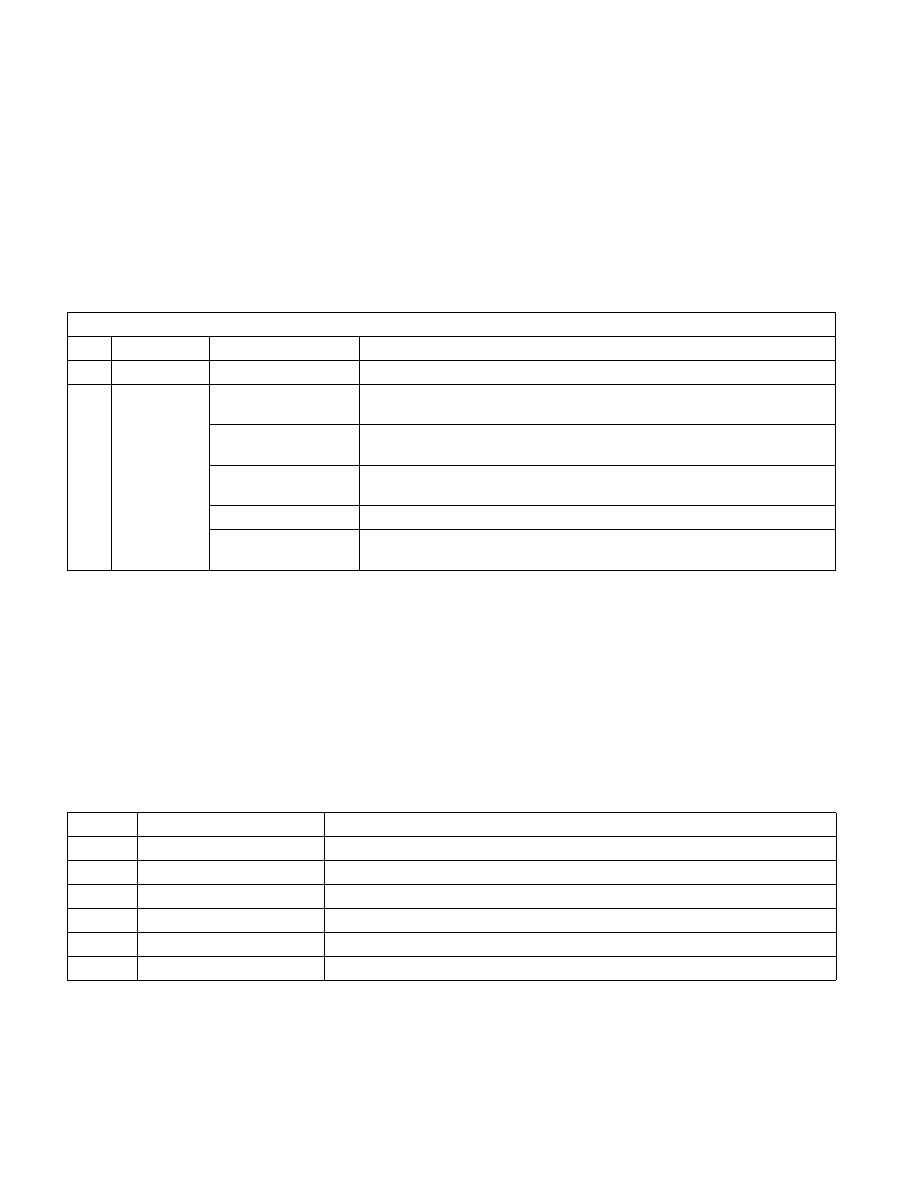

Table 16-5. Incremental MCA Error Code Types for Intel Xeon Processor 7400

Processor MCA_Error_Code (MC6_STATUS[15:0])

Type Error Code

Binary Encoding

Meaning

C

Internal Error

0000 0100 0000 0000 Internal Error Type Code

B

Bus and

Interconnect

Error

0000 100x 0000 1111 Not used but this encoding is reserved for compatibility with other MCA

implementations

0000 101x 0000 1111 Not used but this encoding is reserved for compatibility with other MCA

implementations

0000 110x 0000 1111 Not used but this encoding is reserved for compatibility with other MCA

implementations

0000 1110 0000 1111 Bus and Interconnection Error Type Code

0000 1111 0000 1111 Not used but this encoding is reserved for compatibility with other MCA

implementations

Table 16-6. Type B Bus and Interconnect Error Codes

Bit Num

Sub-Field Name

Description

16

FSB Request Parity

Parity error detected during FSB request phase

19:17

Reserved

20

FSB Hard Fail Response

“Hard Failure“ response received for a local transaction

21

FSB Response Parity

Parity error on FSB response field detected

22

FSB Data Parity

FSB data parity error on inbound data detected

31:23

---

Reserved