Vol. 3B 16-5

INTERPRETING MACHINE-CHECK ERROR CODES

16.2.1 Model-Specific Machine Check Error Codes for Intel Xeon Processor 7400 Series

Intel Xeon processor 7400 series has machine check register banks that generally follows the description of

Chapter 15 and Section 16.2. Additional error codes specific to Intel Xeon processor 7400 series is describe in this

section.

MC4_STATUS[63:0] is the main error logging for the processor’s L3 and front side bus errors for Intel Xeon

processor 7400 series. It supports the L3 Errors, Bus and Interconnect Errors Compound Error Codes in the MCA

Error Code Field.

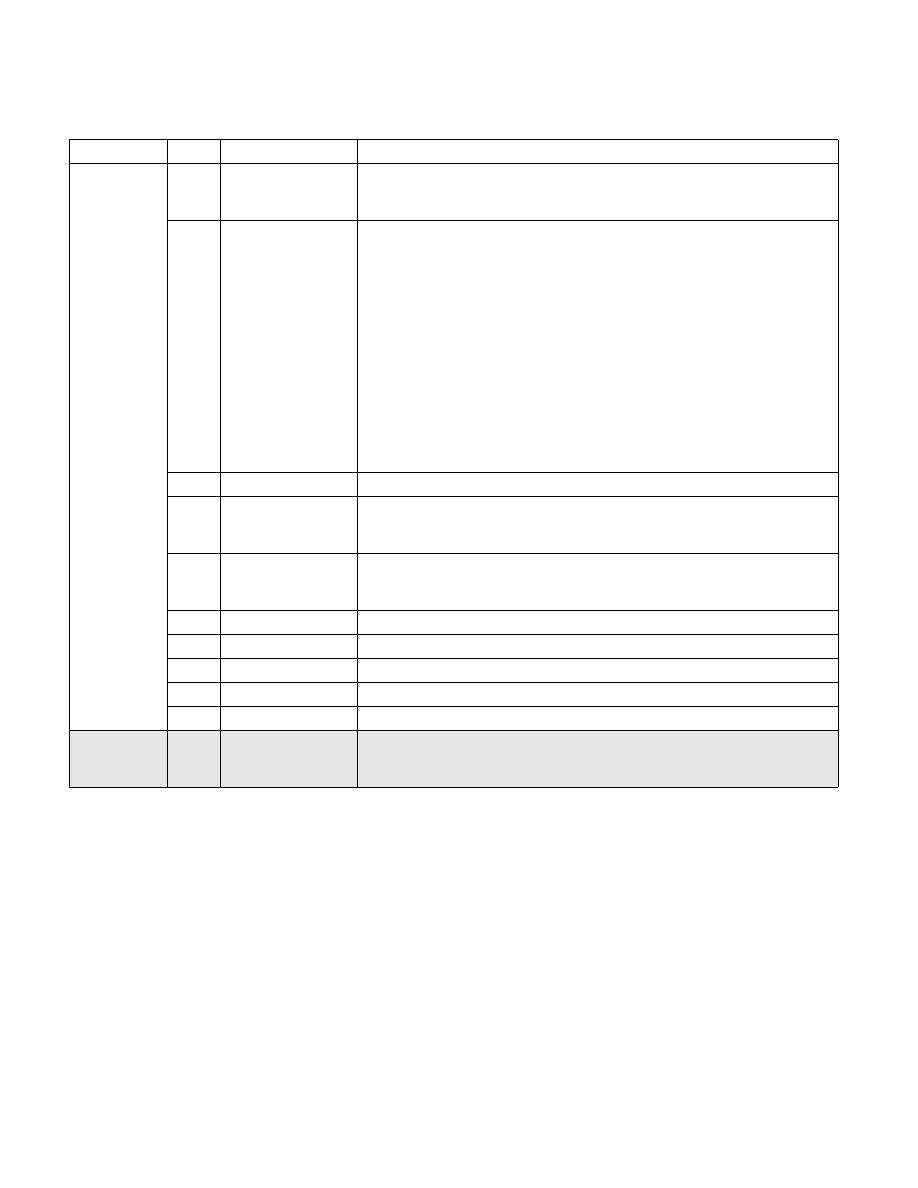

36

Response parity error This bit is asserted in IA32_MCi_STATUS if this component has received a parity

error on the RS[2:0]# pins for a response transaction. The RS signals are checked

by the RSP# external pin.

37

FSB address parity

Address parity error detected:

1 = Address parity error detected

0 = No address parity error

38

Timeout BINIT

This bit is asserted in IA32_MCi_STATUS if this component has experienced a ROB

time-out, which indicates that no micro-instruction has been retired for a

predetermined period of time.

A ROB time-out occurs when the 23-bit ROB time-out counter carries a 1 out of its

high order bit. The timer is cleared when a micro-instruction retires, an exception is

detected by the core processor, RESET is asserted, or when a ROB BINIT occurs.

The ROB time-out counter is prescaled by the 8-bit PIC timer which is a divide by

128 of the bus clock the bus clock is 1:2, 1:3, 1:4 of the core clock). When a carry

out of the 8-bit PIC timer occurs, the ROB counter counts up by one. While this bit

is asserted, it cannot be overwritten by another error.

39-41

Reserved

Reserved

42

Hard error

This bit is asserted in IA32_MCi_STATUS if this component has initiated a bus

transactions which has received a hard error response. While this bit is asserted, it

cannot be overwritten.

43

IERR

This bit is asserted in IA32_MCi_STATUS if this component has experienced a

failure that causes the IERR pin to be asserted. While this bit is asserted, it cannot

be overwritten.

44

Reserved

Reserved

45

Reserved

Reserved

46

Reserved

Reserved

47-54

Reserved

Reserved

55-56

Reserved

Reserved.

Status register

validity

indicators

1

57-63

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

Table 16-4. Incremental Bus Error Codes of Machine Check for Processors

Based on Intel Core Microarchitecture (Contd.)

Type

Bit No. Bit Function

Bit Description