Vol. 3B 16-3

INTERPRETING MACHINE-CHECK ERROR CODES

16.2

INCREMENTAL DECODING INFORMATION: INTEL CORE 2 PROCESSOR

FAMILY MACHINE ERROR CODES FOR MACHINE CHECK

Table 16-4 provides information for interpreting additional model-specific fields for external bus errors relating to

processor based on Intel Core microarchitecture, which implements the P4 bus specification. Table 16-3 lists the

CPUID signatures for Intel 64 processors that are covered by Table 16-4. These errors are reported in the

IA32_MCi_STATUS MSRs. They are reported architecturally as compound errors with a general form of

0000 1PPT RRRR IILL in the MCA error code field. See Chapter 15 for information on the interpretation of

compound error codes.

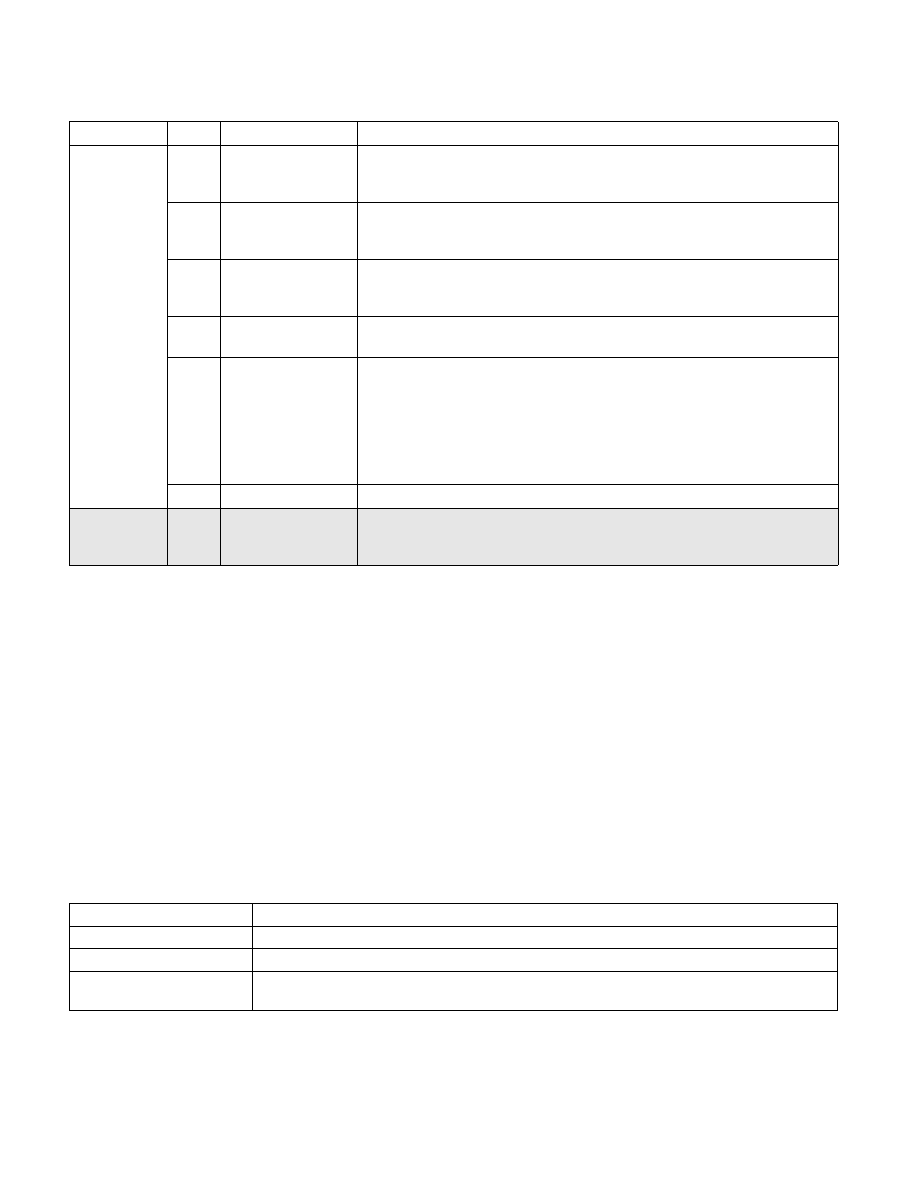

43

IERR

This bit is asserted in IA32_MCi_STATUS if this component has experienced a

failure that causes the IERR pin to be asserted. While this bit is asserted, it cannot

be overwritten.

44

AERR

This bit is asserted in IA32_MCi_STATUS if this component has initiated 2 failing

bus transactions which have failed due to Address Parity Errors AERR asserted).

While this bit is asserted, it cannot be overwritten.

45

UECC

The Uncorrectable ECC error bit is asserted in IA32_MCi_STATUS for uncorrected

ECC errors. While this bit is asserted, the ECC syndrome field will not be

overwritten.

46

CECC

The correctable ECC error bit is asserted in IA32_MCi_STATUS for corrected ECC

errors.

47-54

ECC syndrome

The ECC syndrome field in IA32_MCi_STATUS contains the 8-bit ECC syndrome only

if the error was a correctable/uncorrectable ECC error and there wasn't a previous

valid ECC error syndrome logged in IA32_MCi_STATUS.

A previous valid ECC error in IA32_MCi_STATUS is indicated by

IA32_MCi_STATUS.bit45 uncorrectable error occurred) being asserted. After

processing an ECC error, machine-check handling software should clear

IA32_MCi_STATUS.bit45 so that future ECC error syndromes can be logged.

55-56

Reserved

Reserved.

Status register

validity

indicators

1

57-63

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

2. For processors with a CPUID signature of 06_0EH, a ROB time-out occurs when the 23-bit ROB time-out counter carries a 1 out of its

high order bit.

Table 16-3. CPUID DisplayFamily_DisplayModel Signatures for Processors Based on Intel Core Microarchitecture

DisplayFamily_DisplayModel Processor Families/Processor Number Series

06_1DH

Intel Xeon Processor 7400 series.

06_17H

Intel Xeon Processor 5200, 5400 series, Intel Core 2 Quad processor Q9650.

06_0FH

Intel Xeon Processor 3000, 3200, 5100, 5300, 7300 series, Intel Core 2 Quad, Intel Core 2 Extreme,

Intel Core 2 Duo processors, Intel Pentium dual-core processors.

Table 16-2. Incremental Decoding Information: Processor Family 06H Machine Error Codes For Machine Check

Type

Bit No. Bit Function

Bit Description