15-14 Vol. 3B

MACHINE-CHECK ARCHITECTURE

CMCI interrupt delivery is configured by writing to the LVT CMCI register entry in the local APIC register space at

default address of APIC_BASE + 2F0H. A CMCI interrupt can be delivered to more than one logical processors if

multiple logical processors are affected by the associated MC errors. For example, if a corrected bit error in a cache

shared by two logical processors caused a CMCI, the interrupt will be delivered to both logical processors sharing

that microarchitectural sub-system. Similarly, package level errors may cause CMCI to be delivered to all logical

processors within the package. However, system level errors will not be handled by CMCI.

See Section 10.5.1, “Local Vector Table” for details regarding the LVT CMCI register.

15.5.2

System Software Recommendation for Managing CMCI and Machine Check Resources

System software must enable and manage CMCI, set up interrupt handlers to service CMCI interrupts delivered to

affected logical processors, program CMCI LVT entry, and query machine check banks that are shared by more than

one logical processors.

This section describes techniques system software can implement to manage CMCI initialization, service CMCI

interrupts in a efficient manner to minimize contentions to access shared MSR resources.

15.5.2.1 CMCI Initialization

Although a CMCI interrupt may be delivered to more than one logical processors depending on the nature of the

corrected MC error, only one instance of the interrupt service routine needs to perform the necessary service and

make queries to the machine-check banks. The following steps describes a technique that limits the amount of

work the system has to do in response to a CMCI.

•

To provide maximum flexibility, system software should define per-thread data structure for each logical

processor to allow equal-opportunity and efficient response to interrupt delivery. Specifically, the per-thread

data structure should include a set of per-bank fields to track which machine check bank it needs to access in

response to a delivered CMCI interrupt. The number of banks that needs to be tracked is determined by

IA32_MCG_CAP[7:0].

•

Initialization of per-thread data structure. The initialization of per-thread data structure must be done serially

on each logical processor in the system. The sequencing order to start the per-thread initialization between

different logical processor is arbitrary. But it must observe the following specific detail to satisfy the shared

nature of specific MSR resources:

a. Each thread initializes its data structure to indicate that it does not own any MC bank registers.

b. Each thread examines IA32_MCi_CTL2[30] indicator for each bank to determine if another thread has

already claimed ownership of that bank.

•

If IA32_MCi_CTL2[30] had been set by another thread. This thread can not own bank i and should

proceed to step b. and examine the next machine check bank until all of the machine check banks are

exhausted.

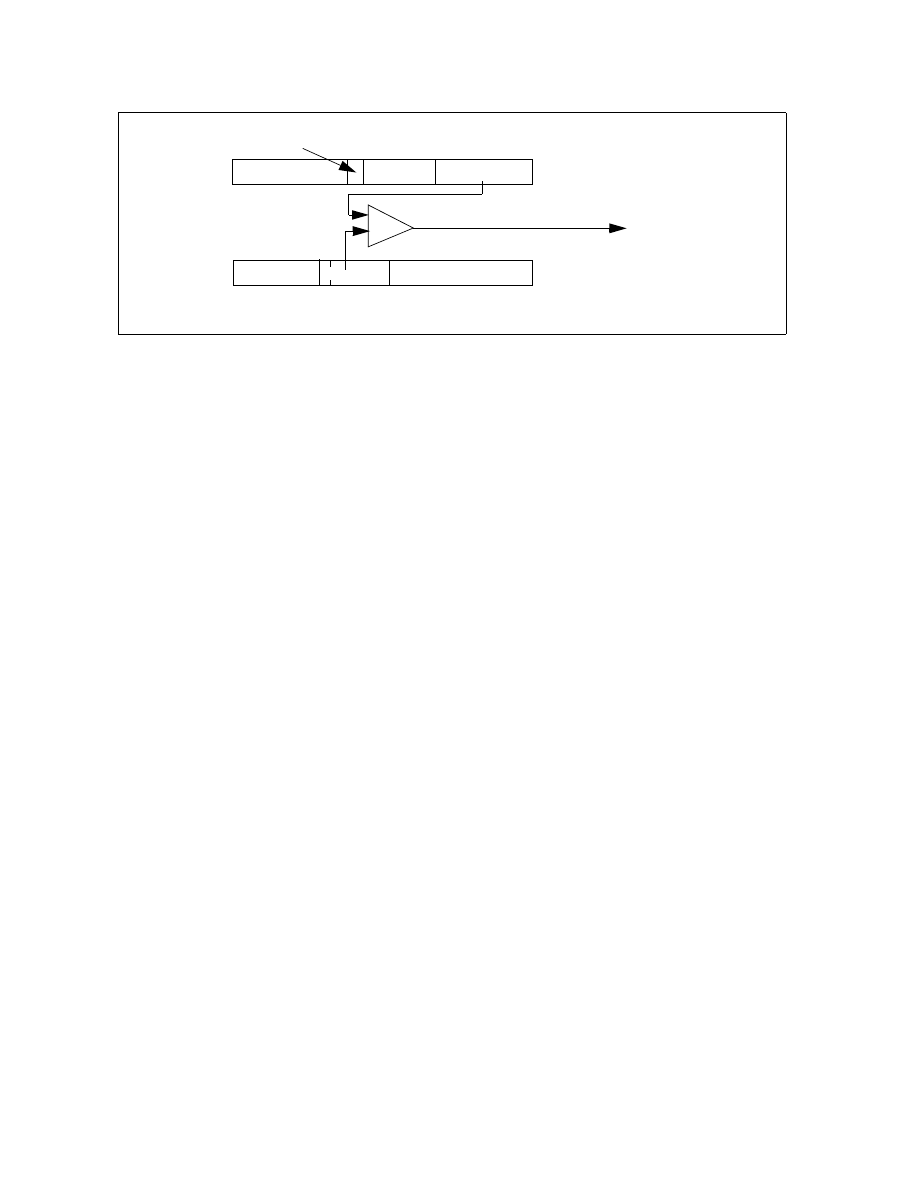

Figure 15-10. CMCI Behavior

Error threshold

63

0

MCi_CTL2

30

31

Error count

53

0

Software write 1 to enable

Count overflow threshold -> CMCI LVT in local APIC

29

14

37

MCi_STATUS

38

52

?=

APIC_BASE + 2F0H