Vol. 3B 15-7

MACHINE-CHECK ARCHITECTURE

•

If IA32_MCG_CAP[10] is 1, bits 52:38 are architectural (not model-specific). In this case, bits 52:38

reports the value of a 15 bit counter that increments each time a corrected error is observed by the MCA

recording bank. This count value will continue to increment until cleared by software. The most

significant bit, 52, is a sticky count overflow bit.

•

If IA32_MCG_CAP[11] is 0, bits 56:53 also contain “Other Information” (in the same sense).

•

If IA32_MCG_CAP[11] is 1, bits 56:53 are architectural (not model-specific). In this case, bits 56:53

have the following functionality:

•

If IA32_MCG_CAP[24] is 0, bits 56:55 are reserved.

•

If IA32_MCG_CAP[24] is 1, bits 56:55 are defined as follows:

•

S (Signaling) flag, bit 56 - Signals the reporting of UCR errors in this MC bank. See Section 15.6.2

for additional detail.

•

AR (Action Required) flag, bit 55 - Indicates (when set) that MCA error code specific recovery

action must be performed by system software at the time this error was signaled. See Section

15.6.2 for additional detail.

•

If the UC bit (Figure 15-6) is 1, bits 54:53 are undefined.

•

If the UC bit (Figure 15-6) is 0, bits 54:53 indicate the status of the hardware structure that

reported the threshold-based error. See Table 15-1.

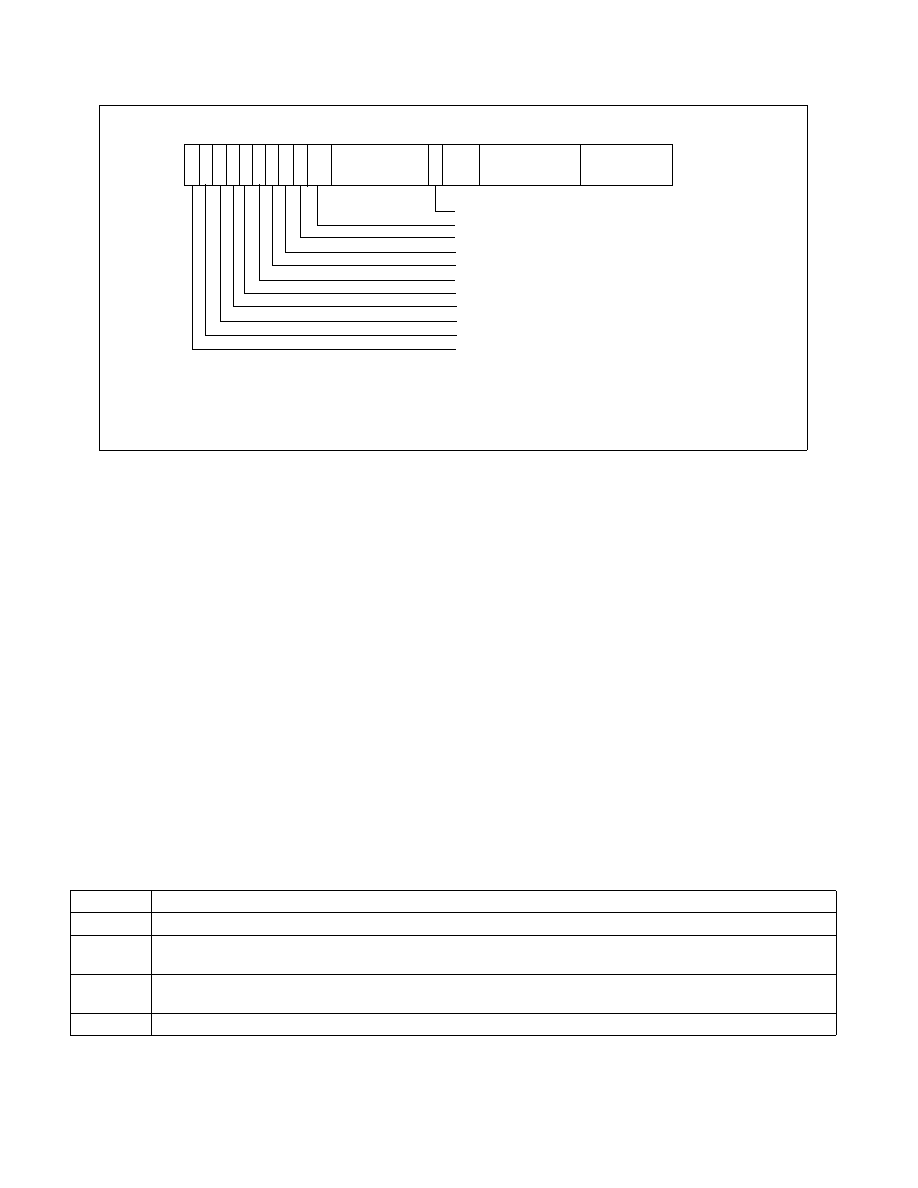

Figure 15-6. IA32_MCi_STATUS Register

Table 15-1. Bits 54:53 in IA32_MCi_STATUS MSRs when IA32_MCG_CAP[11] = 1 and UC = 0

Bits 54:53

Meaning

00

No tracking - No hardware status tracking is provided for the structure reporting this event.

01

Green - Status tracking is provided for the structure posting the event; the current status is green (below threshold).

For more information, see Section 15.4, “Enhanced Cache Error reporting”.

10

Yellow - Status tracking is provided for the structure posting the event; the current status is yellow (above threshold).

For more information, see Section 15.4, “Enhanced Cache Error reporting”.

11

Reserved

63

Threshold-based error status (54:53)**

AR — Recovery action required for UCR error (55)***

S — Signaling an uncorrected recoverable (UCR) error (56)***

PCC — Processor context corrupted (57)

37

32 31

16

0

P

C

A

E

ADDRV — MCi_ADDR register valid (58)

MISCV — MCi_MISC register valid (59)

EN — Error reporting enabled (60)

UC — Uncorrected error (61)

OVER — Error overflow (62)

VAL — MCi_STATUS register valid (63)

C

MCA Error Code

U

S

R

Other

MSCOD Model

54 53

38

62 61 60 59 58 57 56 55

52

15

V

A

L

O

V

E

R

C N

Specific Error Code

Info

Corrected Error

Count

** When IA32_MCG_CAP[11] (MCG_TES_P) is not set, these bits are model-specific

(part of “Other Information”).

*** When IA32_MCG_CAP[11] or IA32_MCG_CAP[24] are not set, these bits are reserved, or

model-specific (part of “Other Information”).

36

* When IA32_MCG_CAP[25] (MCG_EMC_P) is set, bit 37 is not part of “Other Information”.

Firmware updated error status indicator (37)*