Vol. 3A 10-49

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

Cycles 21 through 28 are used to arbitrate for the lowest priority processor. The processors participating in the

arbitration drive their inverted processor priority on the bus. Only the local APICs having free interrupt slots partic-

ipate in the lowest priority arbitration. If no such APIC exists, the message will be rejected, requiring it to be tried

at a later time.

Cycles 29 through 32 are also used for arbitration in case two or more processors have the same lowest priority. In

the lowest priority delivery mode, all combinations of errors in cycle 33 (A2 A2) will set the “accept error” bit in the

error status register (see Figure 10-9). Arbitration priority update is performed in cycle 20, and is not affected by

errors detected in cycle 33. Only the local APIC that wins in the lowest priority arbitration, drives cycle 33. An error

in cycle 33 will force the sender to resend the message.

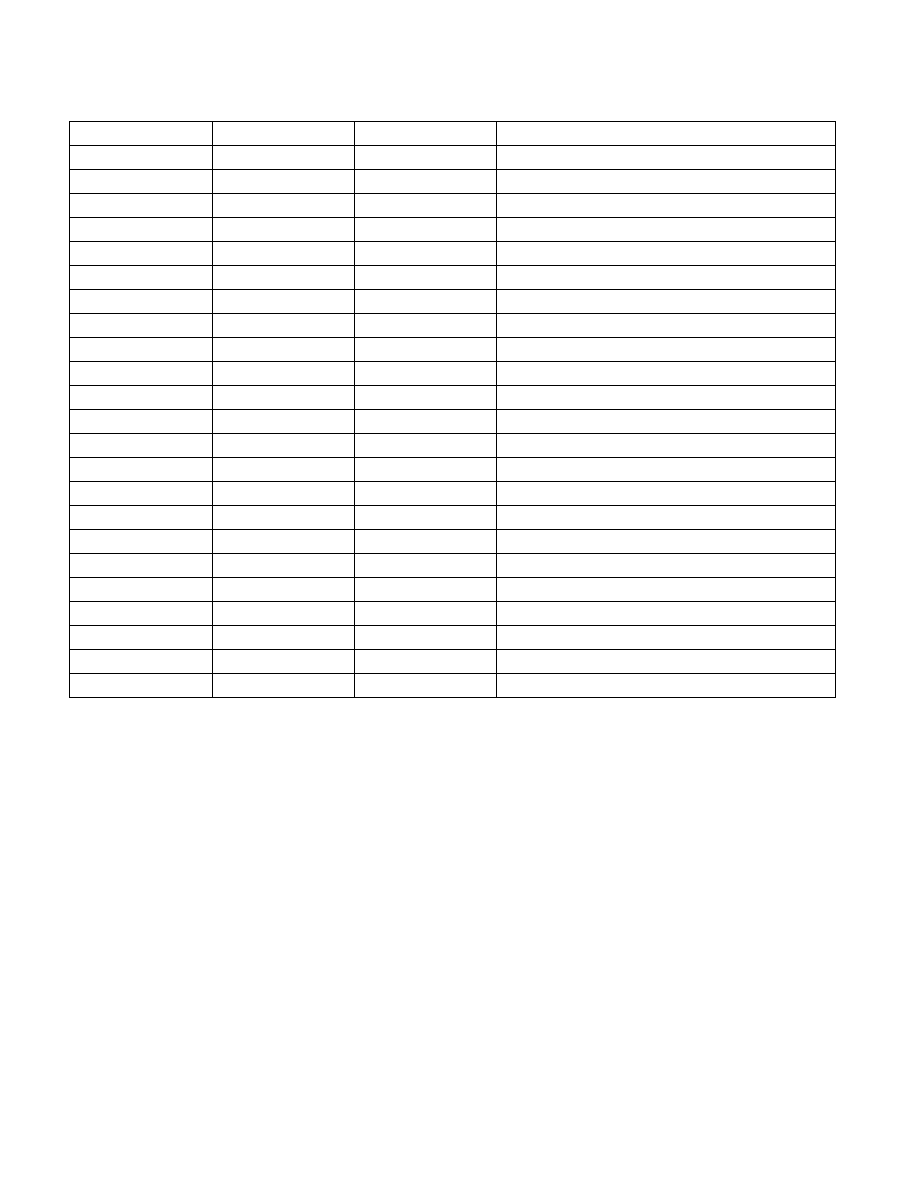

10.13.2.3 APIC Bus Status Cycles

Certain cycles within an APIC bus message are status cycles. During these cycles the status flags (A:A) and

(A1:A1) are examined. Table 10-4 shows how these status flags are interpreted, depending on the current delivery

mode and existence of a focus processor.

12

V1

V0

13

D7

D6

D7-D0 = Destination

14

D5

D4

15

D3

D2

16

D1

D0

17

C

C

Checksum for cycles 6-16

18

0

0

19

A

A

Status cycle 0

20

A1

A1

Status cycle 1

21

P7

0

P7 - P0 = Inverted Processor Priority

22

P6

0

23

P5

0

24

P4

0

25

P3

0

26

P2

0

27

P1

0

28

P0

0

29

ArbID3

0

Arbitration ID 3 -0

30

ArbID2

0

31

ArbID1

0

32

ArbID0

0

33

A2

A2

Status Cycle

34

0

0

Idle

Table 10-3. Non-Focused Lowest Priority Message (34 Cycles) (Contd.)

Cycle

Bit0

Bit1