10-38 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

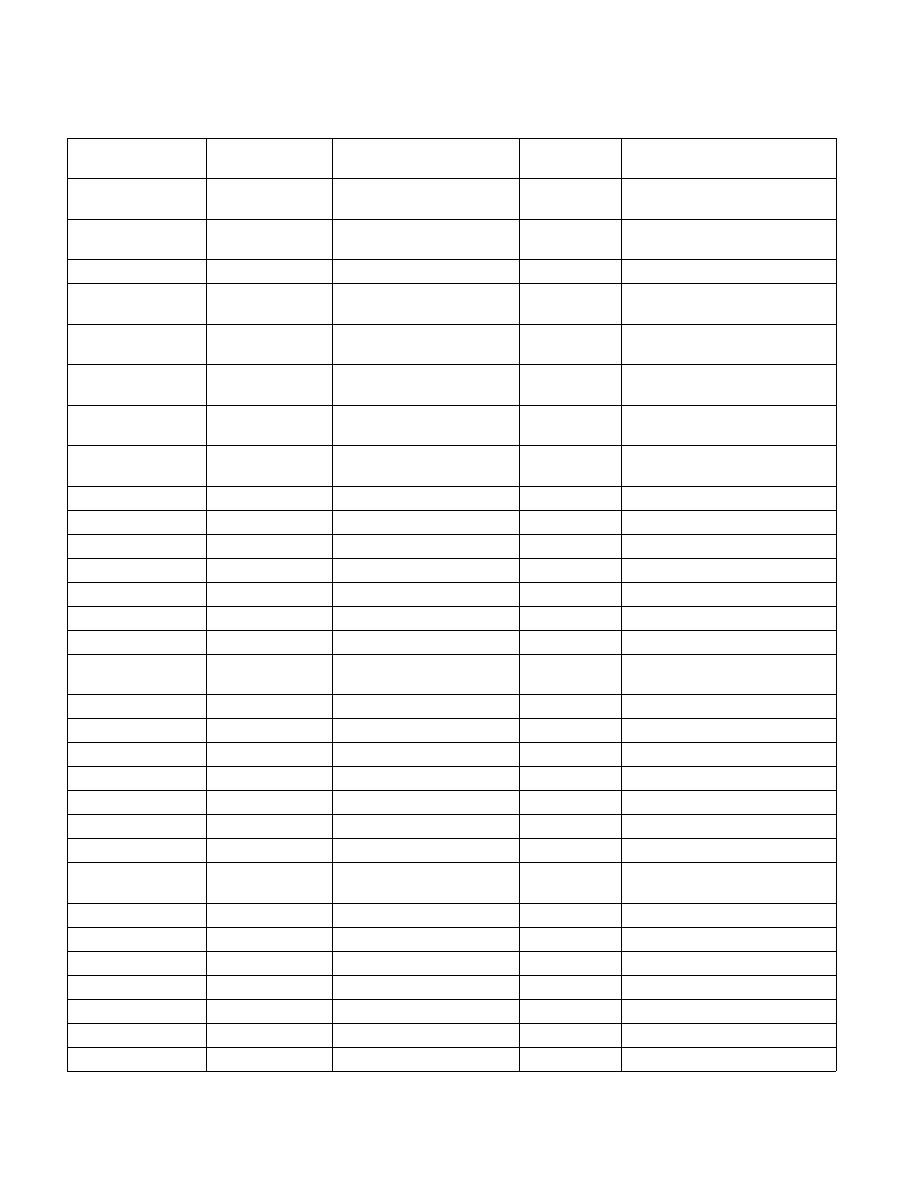

Table 10-6. Local APIC Register Address Map Supported by x2APIC

MSR Address

(x2APIC mode)

MMIO Offset

(xAPIC mode)

Register Name

MSR R/W

Semantics

Comments

802H

020H

Local APIC ID register

Read-only

1

See Section 10.12.5.1 for initial

values.

803H

030H

Local APIC Version register

Read-only

Same version used in xAPIC mode

and x2APIC mode.

808H

080H

Task Priority Register (TPR)

Read/write

Bits 31:8 are reserved.

2

80AH

0A0H

Processor Priority Register

(PPR)

Read-only

80BH

0B0H

EOI register

Write-only

3

WRMSR of a non-zero value causes

#GP(0).

80DH

0D0H

Logical Destination Register

(LDR)

Read-only

Read/write in xAPIC mode.

80FH

0F0H

Spurious Interrupt Vector

Register (SVR)

Read/write

See Section 10.9 for reserved bits.

810H

100H

In-Service Register (ISR); bits

31:0

Read-only

811H

110H

ISR bits 63:32

Read-only

812H

120H

ISR bits 95:64

Read-only

813H

130H

ISR bits 127:96

Read-only

814H

140H

ISR bits 159:128

Read-only

815H

150H

ISR bits 191:160

Read-only

816H

160H

ISR bits 223:192

Read-only

817H

170H

ISR bits 255:224

Read-only

818H

180H

Trigger Mode Register (TMR);

bits 31:0

Read-only

819H

190H

TMR bits 63:32

Read-only

81AH

1A0H

TMR bits 95:64

Read-only

81BH

1B0H

TMR bits 127:96

Read-only

81CH

1C0H

TMR bits 159:128

Read-only

81DH

1D0H

TMR bits 191:160

Read-only

81EH

1E0H

TMR bits 223:192

Read-only

81FH

1F0H

TMR bits 255:224

Read-only

820H

200H

Interrupt Request Register

(IRR); bits 31:0

Read-only

821H

210H

IRR bits 63:32

Read-only

822H

220H

IRR bits 95:64

Read-only

823H

230H

IRR bits 127:96

Read-only

824H

240H

IRR bits 159:128

Read-only

825H

250H

IRR bits 191:160

Read-only

826H

260H

IRR bits 223:192

Read-only

827H

270H

IRR bits 255:224

Read-only