10-34 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

data specifies the message. System software is expected to initialize the message destination and

message during device configuration, allocating one or more non-shared messages to each MSI

capable function.”

The capabilities mechanism provided by the PCI Local Bus Specification is used to identify and configure MSI

capable PCI devices. Among other fields, this structure contains a Message Data Register and a Message Address

Register. To request service, the PCI device function writes the contents of the Message Data Register to the

address contained in the Message Address Register (and the Message Upper Address register for 64-bit message

addresses).

Section 10.11.1 and Section 10.11.2 provide layout details for the Message Address Register and the Message Data

Register. The operation issued by the device is a PCI write command to the Message Address Register with the

Message Data Register contents. The operation follows semantic rules as defined for PCI write operations and is a

DWORD operation.

10.11.1 Message Address Register Format

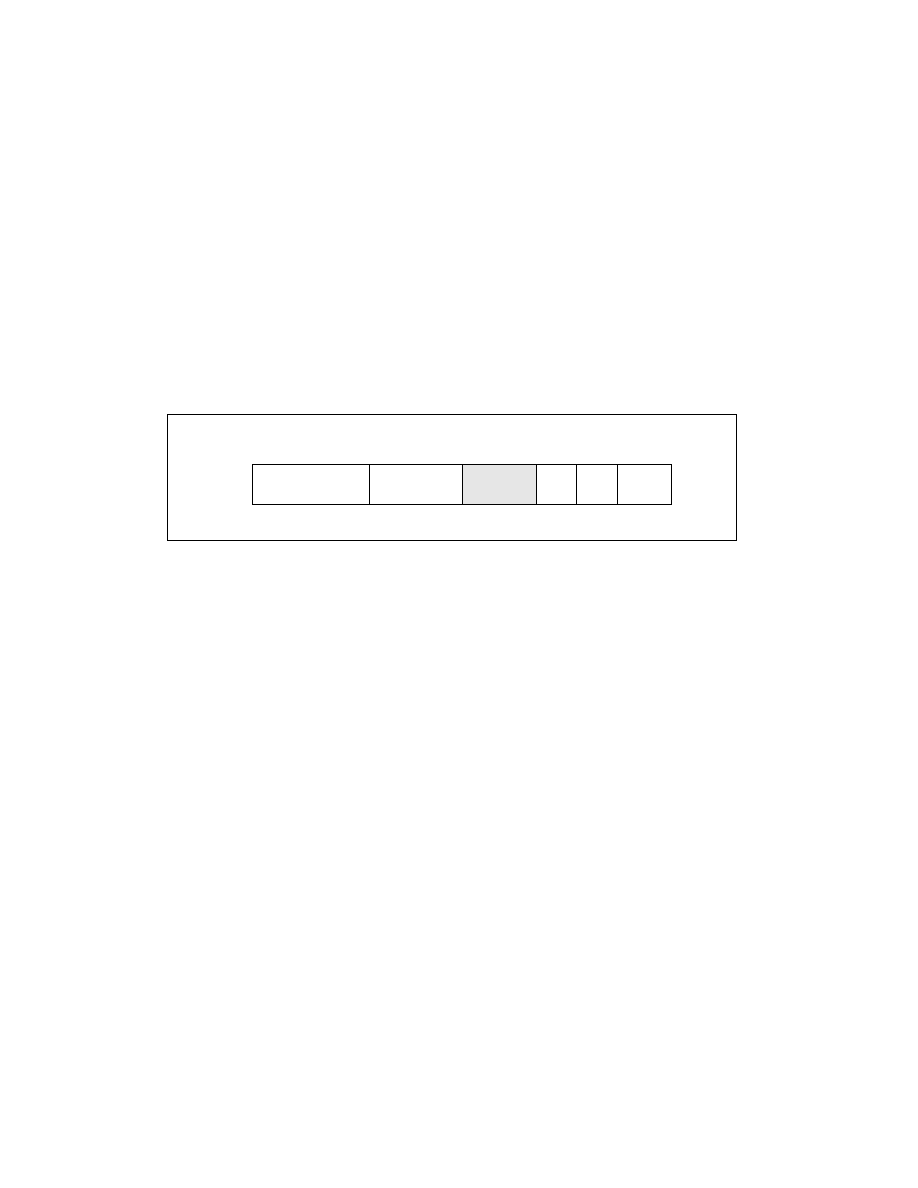

The format of the Message Address Register (lower 32-bits) is shown in Figure 10-24.

Fields in the Message Address Register are as follows:

1. Bits 31-20 — These bits contain a fixed value for interrupt messages (0FEEH). This value locates interrupts at

the 1-MByte area with a base address of 4G – 18M. All accesses to this region are directed as interrupt

messages. Care must to be taken to ensure that no other device claims the region as I/O space.

2. Destination ID — This field contains an 8-bit destination ID. It identifies the message’s target processor(s).

The destination ID corresponds to bits 63:56 of the I/O APIC Redirection Table Entry if the IOAPIC is used to

dispatch the interrupt to the processor(s).

3. Redirection hint indication (RH) — This bit indicates whether the message should be directed to the

processor with the lowest interrupt priority among processors that can receive the interrupt.

•

When RH is 0, the interrupt is directed to the processor listed in the Destination ID field.

•

When RH is 1 and the physical destination mode is used, the Destination ID field must not be set to FFH;

it must point to a processor that is present and enabled to receive the interrupt.

•

When RH is 1 and the logical destination mode is active in a system using a flat addressing model, the

Destination ID field must be set so that bits set to 1 identify processors that are present and enabled to

receive the interrupt.

•

If RH is set to 1 and the logical destination mode is active in a system using cluster addressing model,

then Destination ID field must not be set to FFH; the processors identified with this field must be

present and enabled to receive the interrupt.

4. Destination mode (DM) — This bit indicates whether the Destination ID field should be interpreted as logical

or physical APIC ID for delivery of the lowest priority interrupt. If RH is 1 and DM is 0, the Destination ID field

is in physical destination mode and only the processor in the system that has the matching APIC ID is

considered for delivery of that interrupt (this means no re-direction). If RH is 1 and DM is 1, the Destination ID

Field is interpreted as in logical destination mode and the redirection is limited to only those processors that are

part of the logical group of processors based on the processor’s logical APIC ID and the Destination ID field in

the message. The logical group of processors consists of those identified by matching the 8-bit Destination ID

with the logical destination identified by the Destination Format Register and the Logical Destination Register in

Figure 10-24. Layout of the MSI Message Address Register

31

20 19

12 11

4

3

2

1

0

0FEEH

Destination ID

Reserved

RH

DM

XX