Vol. 3A 10-33

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

tration. After each arbitration cycle (within an arbitration round), only the potential winners keep driving the bus.

By the time all arbitration cycles are completed, there will be only one APIC left driving the bus. Once a winner is

selected, it is granted exclusive use of the bus, and will continue driving the bus to send its actual message.

After each successfully transmitted message, all APICs increase their arbitration priority by 1. The previous winner

(that is, the one that has just successfully transmitted its message) assumes a priority of 0 (lowest). An agent

whose arbitration priority was 15 (highest) during arbitration, but did not send a message, adopts the previous

winner’s arbitration priority, increments by 1.

Note that the arbitration protocol described above is slightly different if one of the APICs issues a special End-Of-

Interrupt (EOI). This high-priority message is granted the bus regardless of its sender’s arbitration priority, unless

more than one APIC issues an EOI message simultaneously. In the latter case, the APICs sending the EOI

messages arbitrate using their arbitration priorities.

If the APICs are set up to use “lowest priority” arbitration (see Section 10.6.2.4, “Lowest Priority Delivery Mode”)

and multiple APICs are currently executing at the lowest priority (the value in the APR register), the arbitration

priorities (unique values in the Arb ID register) are used to break ties. All 8 bits of the APR are used for the lowest

priority arbitration.

10.10.1 Bus Message Formats

See Section 10.13, “APIC Bus Message Formats,” for a description of bus message formats used to transmit

messages on the serial APIC bus.

10.11 MESSAGE SIGNALLED INTERRUPTS

The PCI Local Bus Specification, Rev 2.2 (www.pcisig.com) introduces the concept of message signalled interrupts.

As the specification indicates:

“Message signalled interrupts (MSI) is an optional feature that enables PCI devices to request

service by writing a system-specified message to a system-specified address (PCI DWORD memory

write transaction). The transaction address specifies the message destination while the transaction

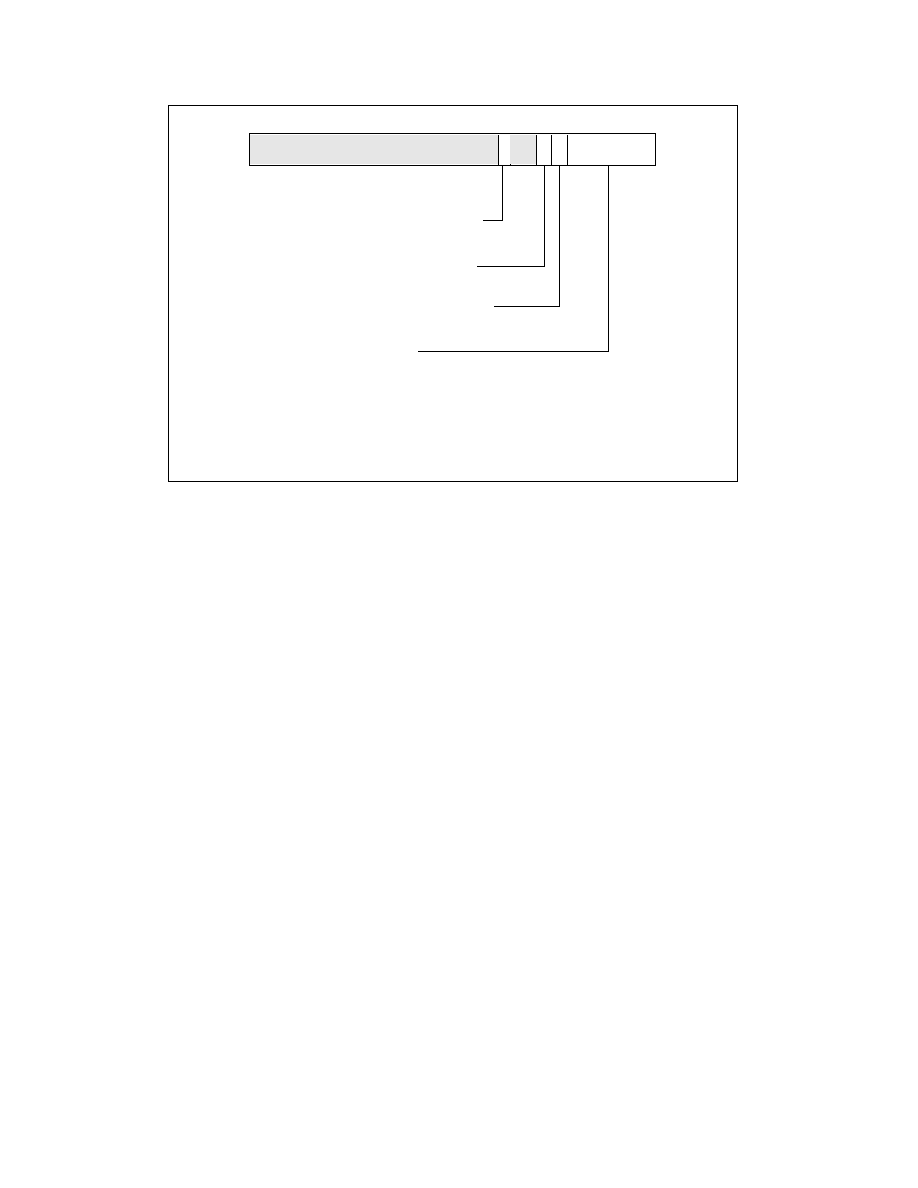

Figure 10-23. Spurious-Interrupt Vector Register (SVR)

31

0

Reserved

7

Focus Processor Checking

2

APIC Software Enable/Disable

8

9

10

0: APIC Disabled

1: APIC Enabled

Spurious Vector

3

Address: FEE0 00F0H

Value after reset: 0000 00FFH

0: Enabled

1: Disabled

1. Not supported on all processors.

2. Not supported in Pentium 4 and Intel Xeon processors.

3. For the P6 family and Pentium processors, bits 0 through 3

are always 0.

11

12

EOI-Broadcast Suppression

1

0: Disabled

1: Enabled