Vol. 3A 10-5

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

NOTE

For P6 family, Pentium 4, and Intel Xeon processors, the APIC handles all memory accesses to

addresses within the 4-KByte APIC register space internally and no external bus cycles are

produced. For the Pentium processors with an on-chip APIC, bus cycles are produced for accesses

to the APIC register space. Thus, for software intended to run on Pentium processors, system

software should explicitly not map the APIC register space to regular system memory. Doing so can

result in an invalid opcode exception (#UD) being generated or unpredictable execution.

Table 10-1 shows how the APIC registers are mapped into the 4-KByte APIC register space. Registers are 32 bits,

64 bits, or 256 bits in width; all are aligned on 128-bit boundaries. All 32-bit registers should be accessed using

128-bit aligned 32-bit loads or stores. Some processors may support loads and stores of less than 32 bits to some

of the APIC registers. This is model specific behavior and is not guaranteed to work on all processors. Any

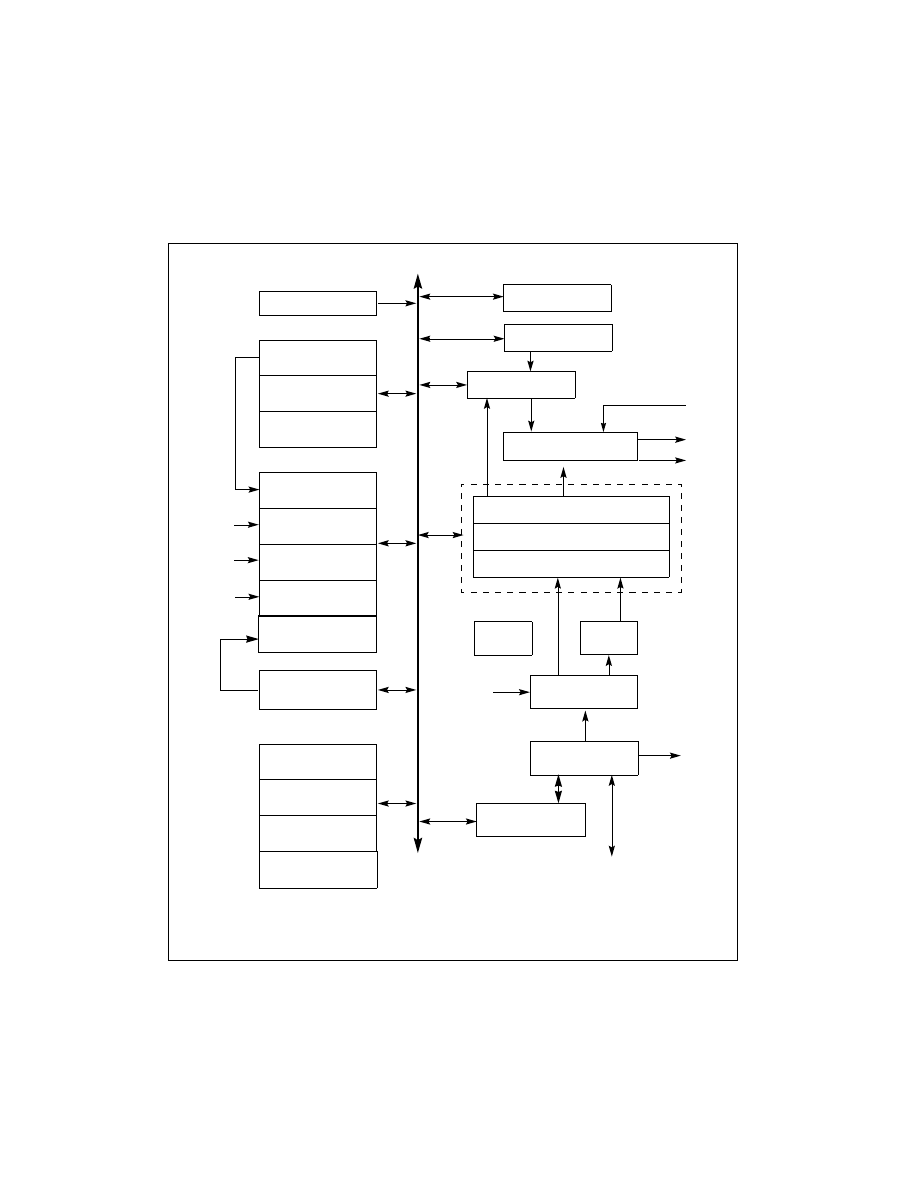

Figure 10-4. Local APIC Structure

Current Count

Register

Initial Count

Register

Divide Configuration

Register

Version Register

Error Status

Register

In-Service Register (ISR)

Vector

Decode

Interrupt Command

Register (ICR)

Acceptance

Logic

Vec[3:0]

& TMR Bit

Register

Select

INIT

NMI

SMI

Protocol

Translation Logic

Dest. Mode

& Vector

Processor System Bus

3

APIC ID

Register

Logical Destination

Register

Destination Format

Register

Timer

Local

Interrupts 0,1

Performance

Monitoring Counters

1

Error

Timer

Local Vector Table

DATA/ADDR

Prioritizer

Task Priority Register

EOI Register

INTR

EXTINT

INTA

LINT0/1

1. Introduced in P6 family processors.

Thermal Sensor

2

2. Introduced in the Pentium 4 and Intel Xeon processors.

Perf. Mon.

Thermal

(Internal

Interrupt)

Sensor

(Internal

Interrupt)

Spurious Vector

Register

Local

Interrupts

3. Three-wire APIC bus in P6 family and Pentium processors.

To

CPU

Core

From

CPU

Core

Interrupt Request Register (IRR)

Trigger Mode Register (TMR)

To

CPU

Core

Processor Priority

Register

4. Not implemented in Pentium 4 and Intel Xeon processors.

Arb. ID

Register

4