Vol. 3A 9-27

PROCESSOR MANAGEMENT AND INITIALIZATION

);

END

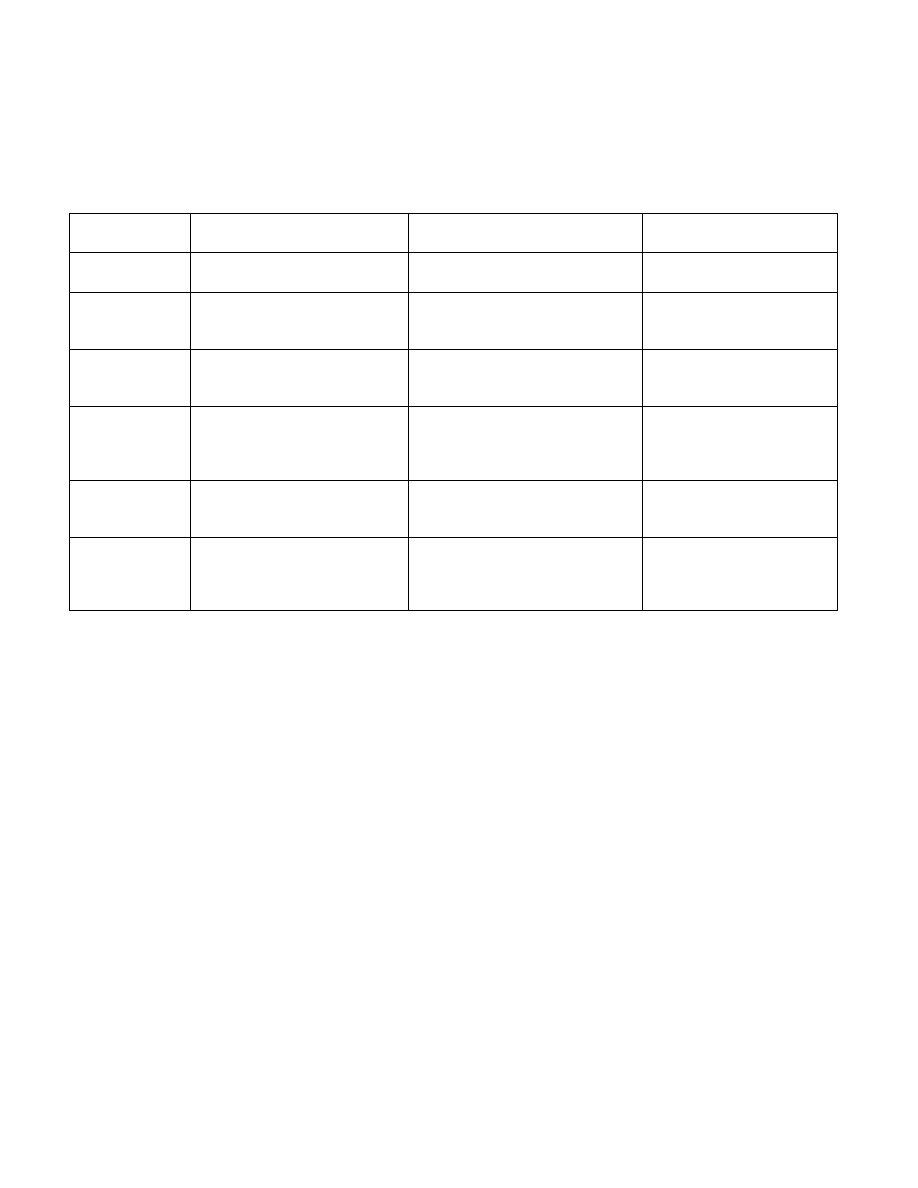

Table 9-6 shows the relationship of each build item with an ASM source file.

9.11

MICROCODE UPDATE FACILITIES

The P6 family and later processors have the capability to correct errata by loading an Intel-supplied data block into

the processor. The data block is called a microcode update. This section describes the mechanisms the BIOS needs

to provide in order to use this feature during system initialization. It also describes a specification that permits the

incorporation of future updates into a system BIOS.

Intel considers the release of a microcode update for a silicon revision to be the equivalent of a processor stepping

and completes a full-stepping level validation for releases of microcode updates.

A microcode update is used to correct errata in the processor. The BIOS, which has an update loader, is responsible

for loading the update on processors during system initialization (Figure 9-7). There are two steps to this process:

the first is to incorporate the necessary update data blocks into the BIOS; the second is to load update data blocks

into the processor.

Table 9-6. Relationship Between BLD Item and ASM Source File

Item

ASM386 and Startup.A58

BLD386 Controls

and BLD file

Effect

Bootstrap

public startup

startup:

bootstrap

start(startup)

Near jump at 0FFFFFFF0H to

start.

GDT location

public GDT_EPROM

GDT_EPROM TABLE_REG <>

TABLE

GDT(location = GDT_EPROM)

The location of the GDT will be

programmed into the

GDT_EPROM location.

IDT location

public IDT_EPROM

IDT_EPROM TABLE_REG <>

TABLE

IDT(location = IDT_EPROM

The location of the IDT will be

programmed into the

IDT_EPROM location.

RAM start

RAM_START equ 400H

memory (reserve = (0..3FFFH))

RAM_START is used as the ram

destination for moving the

tables. It must be excluded from

the application's segment area.

Location of the

application TSS in

the GDT

TSS_INDEX EQU 10

TABLE GDT(

ENTRY = (10: PROTECTED_MODE_

TASK))

Put the descriptor of the

application TSS in GDT entry 10.

EPROM size and

location

size and location of the initialization

code

SEGMENT startup.code (base =

0FFFF0000H) ...memory (RANGE(

ROM_AREA = ROM(x..y))

Initialization code size must be

less than 64K and resides at

upper most 64K of the 4-GByte

memory space.