8-36 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

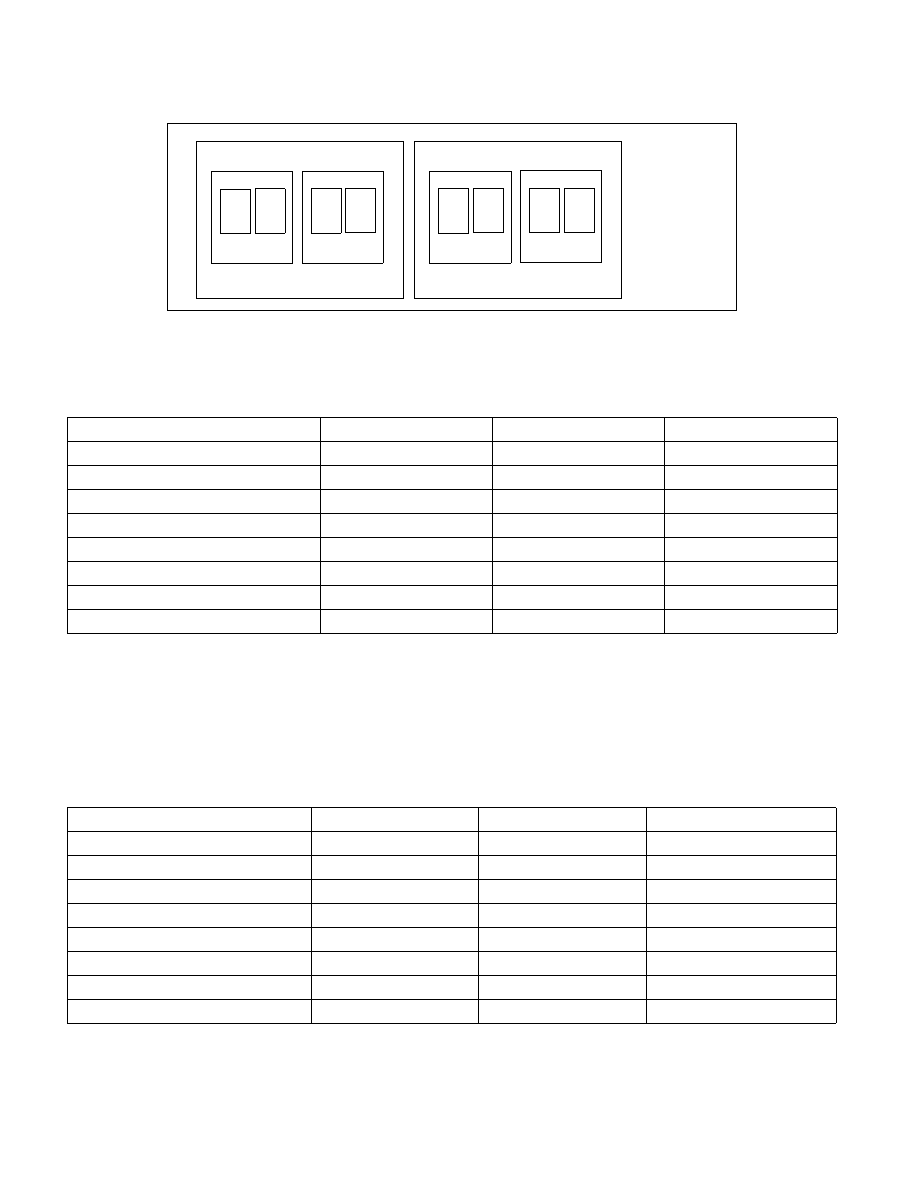

Table 8-3 shows the initial APIC IDs for a hypothetical situation with a dual processor system. Each physical

package providing two processor cores, and each processor core also supporting Intel Hyper-Threading Tech-

nology.

Figure 8-7. Topological Relationships between Hierarchical IDs in a Hypothetical MP Platform

Table 8-2. Initial APIC IDs for the Logical Processors in a System that has Four Intel Xeon MP Processors Supporting

Intel Hyper-Threading Technology

1

Initial APIC ID

Package ID

Core ID

SMT ID

0H

0H

0H

0H

1H

0H

0H

1H

2H

1H

0H

0H

3H

1H

0H

1H

4H

2H

0H

0H

5H

2H

0H

1H

6H

3H

0H

0H

7H

3H

0H

1H

NOTE:

1. Because information on the number of processor cores in a physical package was not available in early single-core processors sup-

porting Intel Hyper-Threading Technology, the core ID can be treated as 0.

Table 8-3. Initial APIC IDs for the Logical Processors in a System that has Two Physical Processors Supporting Dual-

Core and Intel Hyper-Threading Technology

Initial APIC ID

Package ID

Core ID

SMT ID

0H

0H

0H

0H

1H

0H

0H

1H

2H

0H

1H

0H

3H

0H

1H

1H

4H

1H

0H

0H

5H

1H

0H

1H

6H

1H

1H

0H

7H

1H

1H

1H

Package 0

Core 0

T0

T1

Core1

T0

T1

Package 1

Core 0

T0

T1

Core1

T0

T1

SMT_ID

Core ID

Package ID