8-34 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

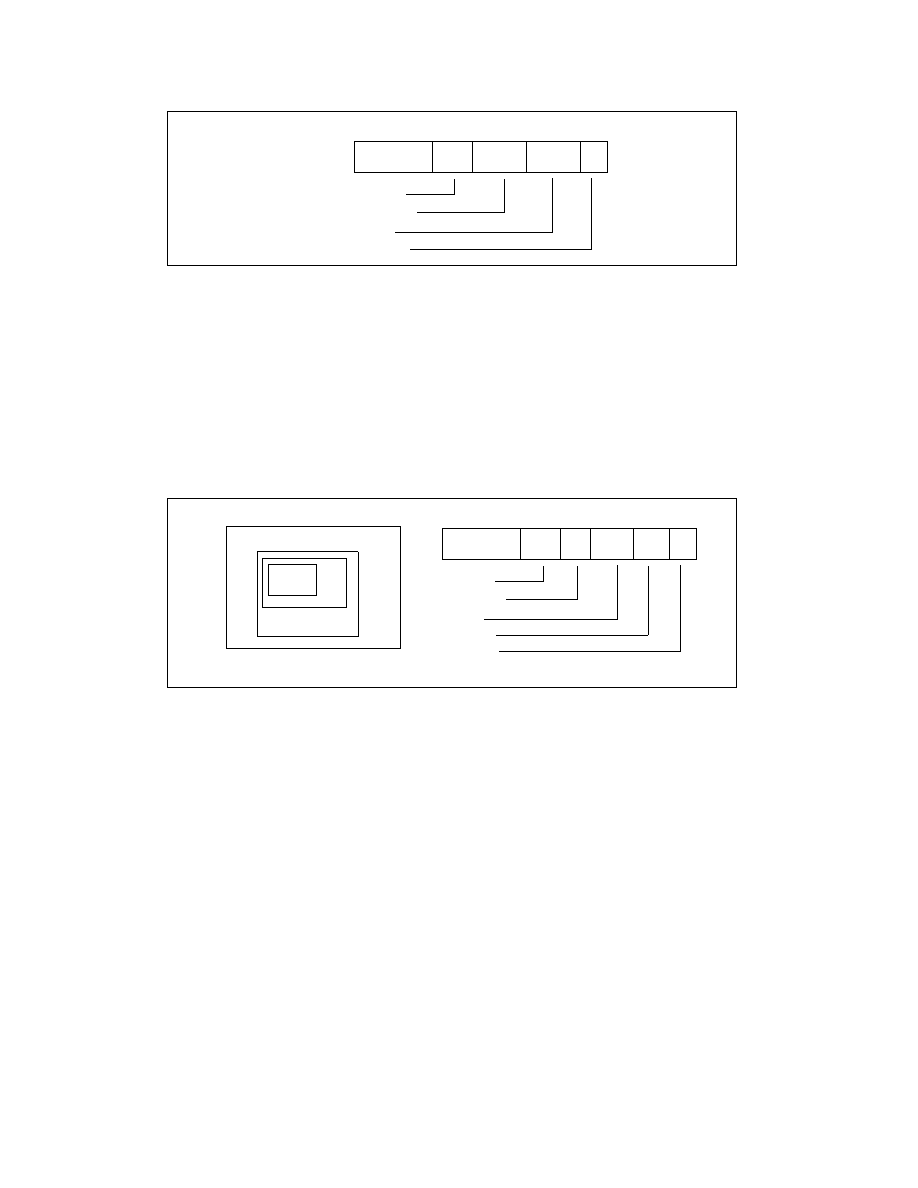

If the processor supports CPUID leaf 0BH, the 32-bit APIC ID can represent cluster plus several levels of topology

within the physical processor package. The exact number of hierarchical levels within a physical processor package

must be enumerated through CPUID leaf 0BH. Common processor families may employ topology similar to that

represented by 8-bit Initial APIC ID. In general, CPUID leaf 0BH can support topology enumeration algorithm that

decompose a 32-bit APIC ID into more than four sub-fields (see Figure 8-6).

The width of each sub-field depends on hardware and software configurations. Field widths can be determined at

runtime using the algorithm discussed below (Example 8-16 through Example 8-20).

Figure 7-6 depicts the relationships of three of the hierarchical sub-fields in a hypothetical MP system. The value of

valid APIC_IDs need not be contiguous across package boundary or core boundaries.

8.9.2

Hierarchical Mapping of CPUID Extended Topology Leaf

CPUID leaf 0BH provides enumeration parameters for software to identify each hierarchy of the processor topology

in a deterministic manner. Each hierarchical level of the topology starting from the SMT level is represented numer-

ically by a sub-leaf index within the CPUID 0BH leaf. Each level of the topology is mapped to a sub-field in the APIC

ID, following the general relationship depicted in Figure 8-6. This mechanism allows software to query the exact

number of levels within a physical processor package and the bit-width of each sub-field of x2APIC ID directly. For

example,

•

Starting from sub-leaf index 0 and incrementing ECX until CPUID.(EAX=0BH, ECX=N):ECX[15:8] returns an

invalid “level type” encoding. The number of levels within the physical processor package is “N” (excluding

PACKAGE). Using Figure 8-6 as an example, CPUID.(EAX=0BH, ECX=3):ECX[15:8] will report 00H, indicating

sub leaf 03H is invalid. This is also depicted by a pseudo code example:

Figure 8-5. Generalized Four level Interpretation of the APIC ID

Figure 8-6. Conceptual Five-level Topology and 32-bit APIC ID Composition

0

Package ID

SMT ID

X

Cluster ID

Reserved

Core ID

X=31 if x2APIC is supported

Otherwise X= 7

0

Package ID

R ID

31

Cluster ID

Reserved

Q ID

SMT ID

R

SMT

Q

Package

Physical Processor Topology

32-bit APIC ID Composition