8-22 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

16. Reads and evaluates the COUNT variable and establishes a processor count.

17. If necessary, reconfigures the APIC and continues with the remaining system diagnostics as appropriate.

8.4.4.2

Typical AP Initialization Sequence

When an AP receives the SIPI, it begins executing BIOS AP initialization code at the vector encoded in the SIPI. The

AP initialization code typically performs the following operations:

1. Waits on the BIOS initialization Lock Semaphore. When control of the semaphore is attained, initialization

continues.

2. Loads the microcode update into the processor.

3. Initializes the MTRRs (using the same mapping that was used for the BSP).

4. Enables the cache.

5. Executes the CPUID instruction with a value of 0H in the EAX register, then reads the EBX, ECX, and EDX

registers to determine if the AP is “GenuineIntel.”

6. Executes the CPUID instruction with a value of 1H in the EAX register, then saves the values in the EAX, ECX,

and EDX registers in a system configuration space in RAM for use later.

7. Switches to protected mode and ensures that the APIC address space is mapped to the strong uncacheable

(UC) memory type.

8. Determines the AP’s APIC ID from the local APIC ID register, and adds it to the MP and ACPI tables and

optionally to the system configuration space in RAM.

9. Initializes and configures the local APIC by setting bit 8 in the SVR register and setting up the LVT3 (error LVT)

for error handling (as described in steps 9 and 10 in Section 8.4.4.1, “Typical BSP Initialization Sequence”).

10. Configures the APs SMI execution environment. (Each AP and the BSP must have a different SMBASE address.)

11. Increments the COUNT variable by 1.

12. Releases the semaphore.

13. Executes one of the following:

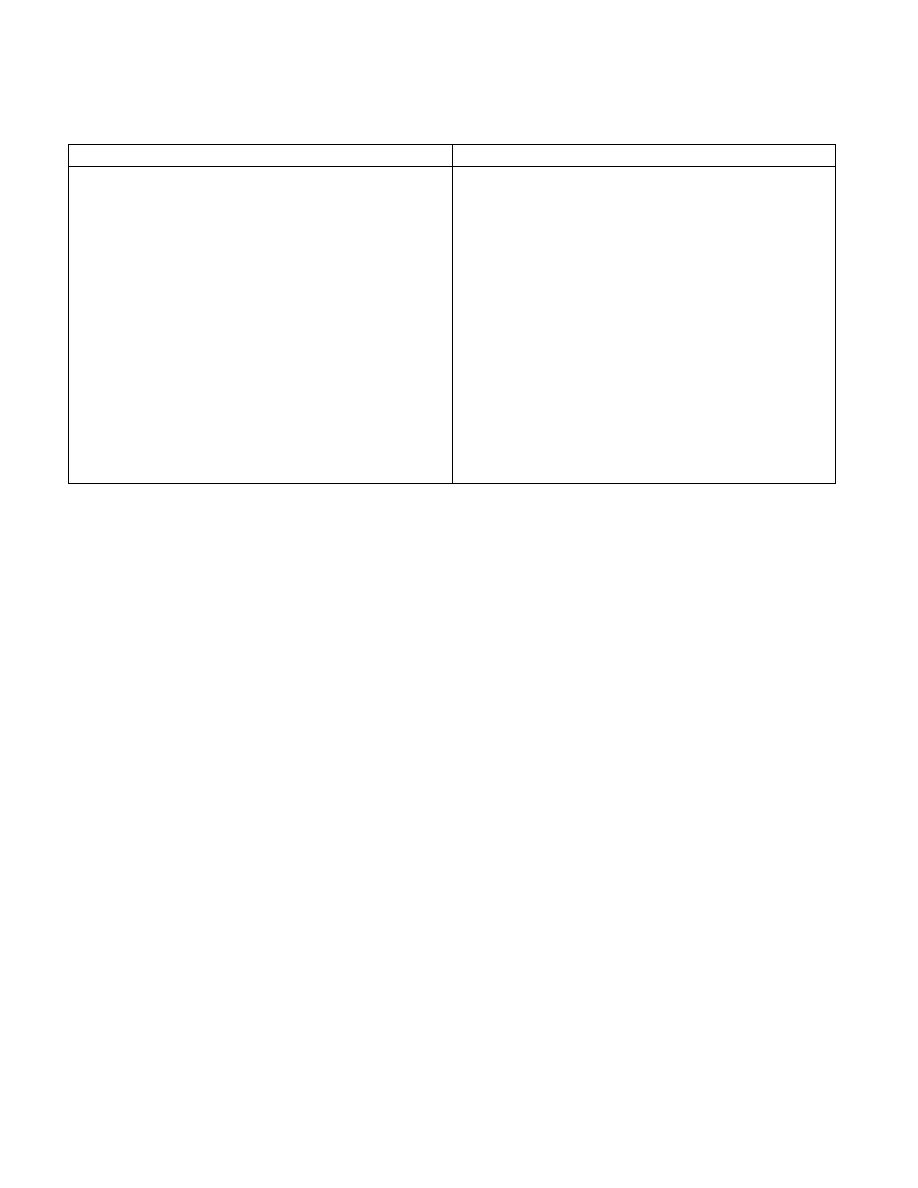

Table 8-1. Broadcast INIT-SIPI-SIPI Sequence and Choice of Timeouts

INIT-SIPI-SIPI when the expected processor count is unknown

INIT-SIPI-SIPI when the expected processor count is known

MOV ESI, ICR_LOW; Load address of ICR low dword into ESI.

MOV EAX, 000C4500H; Load ICR encoding for broadcast INIT IPI

; to all APs into EAX.

MOV [ESI], EAX; Broadcast INIT IPI to all APs

; 10-millisecond delay loop.

MOV EAX, 000C46XXH; Load ICR encoding for broadcast SIPI IP

; to all APs into EAX, where xx is the vector computed in step 10.

MOV [ESI], EAX; Broadcast SIPI IPI to all APs

; 200-microsecond delay loop

MOV [ESI], EAX; Broadcast second SIPI IPI to all APs

;Waits for the timer interrupt until the timer expires

MOV ESI, ICR_LOW; Load address of ICR low dword into ESI.

MOV EAX, 000C4500H; Load ICR encoding for broadcast INIT IPI

; to all APs into EAX.

MOV [ESI], EAX; Broadcast INIT IPI to all APs

; 10-millisecond delay loop.

MOV EAX, 000C46XXH; Load ICR encoding for broadcast SIPI IP

; to all APs into EAX, where xx is the vector computed in step 10.

MOV [ESI], EAX; Broadcast SIPI IPI to all APs

; 200 microsecond delay loop with check to see if COUNT has

; reached the expected processor count. If COUNT reaches

; expected processor count, cancel timer and go to step 16.

MOV [ESI], EAX; Broadcast second SIPI IPI to all APs

; Wait for the timer interrupt polling COUNT. If COUNT reaches

; expected processor count, cancel timer and go to step 16.

; If timer expires, go to step 16.