8-14 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

It is possible for processor 1 to perceive that the repeated string stores in processor 0 are happening out of order.

Assume that fast string operations are enabled on processor 0.

In Example 8-12, processor 0 does two separate rounds of rep stosd operation of 128 doubleword stores, writing

the value 1 (value in EAX) into the first block of 512 bytes from location _x (kept in ES:EDI) in ascending order. It

then writes 1 into a second block of memory from (_x+512) to (_x+1023). All of the memory locations initially

contain 0. The block of memory initially contained 0. Processor 1 performs two load operations from the two blocks

of memory.

It is not possible in the above example for processor 1 to perceive any of the stores from the later string operation

(to the second 512 block) in processor 0 before seeing the stores from the earlier string operation to the first 512

block.

The above example assumes that writes to the second block (_x+512 to _x+1023) does not get executed while

processor 0’s string operation to the first block has been interrupted. If the string operation to the first block by

processor 0 is interrupted, and a write to the second memory block is executed by the interrupt handler, then that

change in the second memory block will be visible before the string operation to the first memory block resumes.

In Example 8-13, processor 0 does one round of (128 iterations) doubleword string store operation via rep:stosd,

writing the value 1 (value in EAX) into a block of 512 bytes from location _x (kept in ES:EDI) in ascending order. It

then writes to a second memory location outside the memory block of the previous string operation. Processor 1

performs two read operations, the first read is from an address outside the 512-byte block but to be updated by

processor 0, the second ready is from inside the block of memory of string operation.

Processor 1 cannot perceive the later store by processor 0 until it sees all the stores from the string operation.

Example 8-13 assumes that processor 0’s store to [_z] is not executed while the string operation has been inter-

rupted. If the string operation is interrupted and the store to [_z] by processor 0 is executed by the interrupt

handler, then changes to [_z] will become visible before the string operation resumes.

Example 8-14 illustrates the visibility principle when a string operation is interrupted.

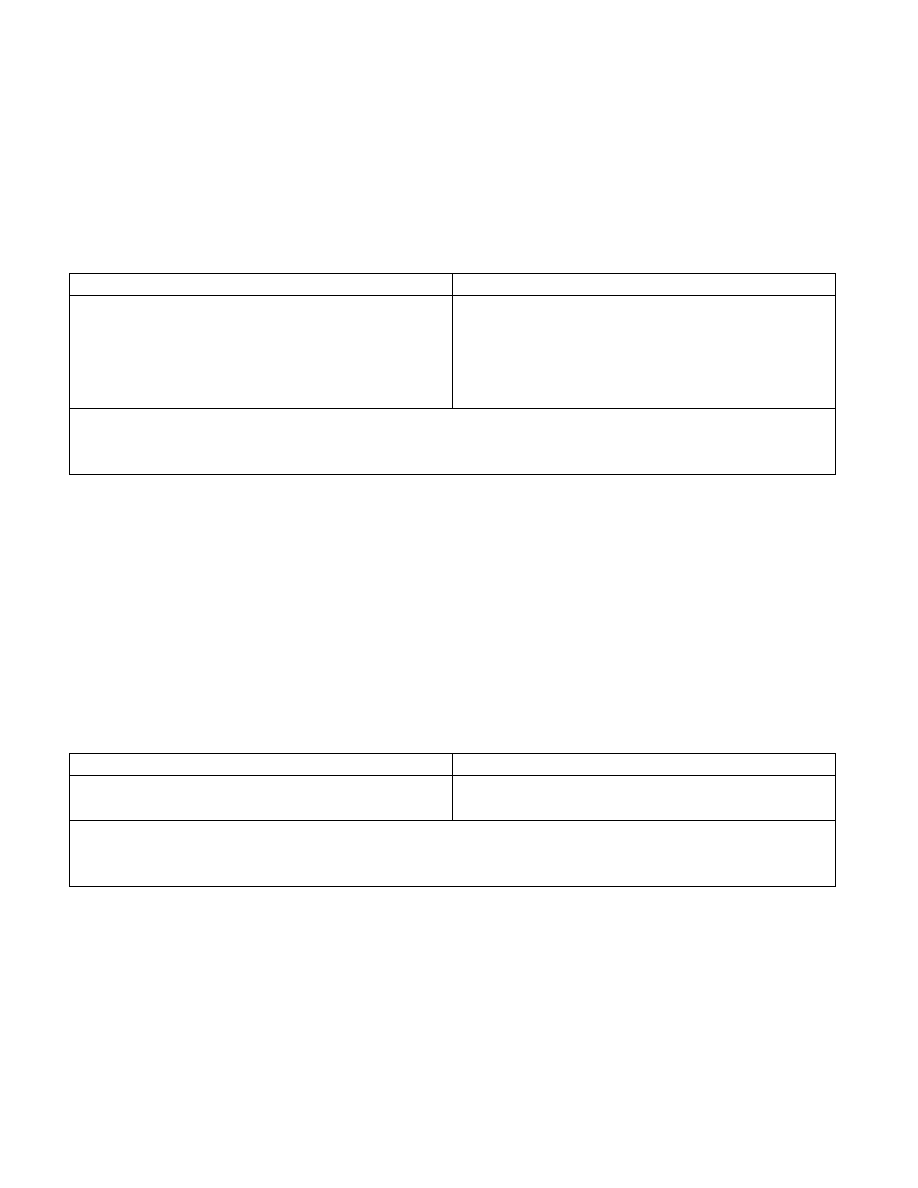

Example 8-12. Stores Across String Operations Are not Reordered

Processor 0

Processor 1

rep:stosd [ _x]

mov r1, [ _z]

mov ecx, $128

mov r2, [ _y]

rep:stosd 512[ _x]

Initially on processor 0: EAX = 1, ECX=128, ES:EDI =_x

Initially [_x] to 1023[_x]= 0, _x <= _y < _x+512 < _z < _x+1024

r1 = 1 and r2 = 0 is not allowed

Example 8-13. String Operations Are not Reordered with later Stores

Processor 0

Processor 1

rep:stosd [ _x]

mov r1, [ _z]

mov [_z], $1

mov r2, [ _y]

Initially on processor 0: EAX = 1, ECX=128, ES:EDI =_x

Initially [_y] = [_z] = 0, [_x] to 511[_x]= 0, _x <= _y < _x+512, _z is a separate memory location

r1 = 1 and r2 = 0 is not allowed