Vol. 3A 8-7

MULTIPLE-PROCESSOR MANAGEMENT

In a multiple-processor system, the following ordering principles apply:

•

Individual processors use the same ordering principles as in a single-processor system.

•

Writes by a single processor are observed in the same order by all processors.

•

Writes from an individual processor are NOT ordered with respect to the writes from other processors.

•

Memory ordering obeys causality (memory ordering respects transitive visibility).

•

Any two stores are seen in a consistent order by processors other than those performing the stores

•

Locked instructions have a total order.

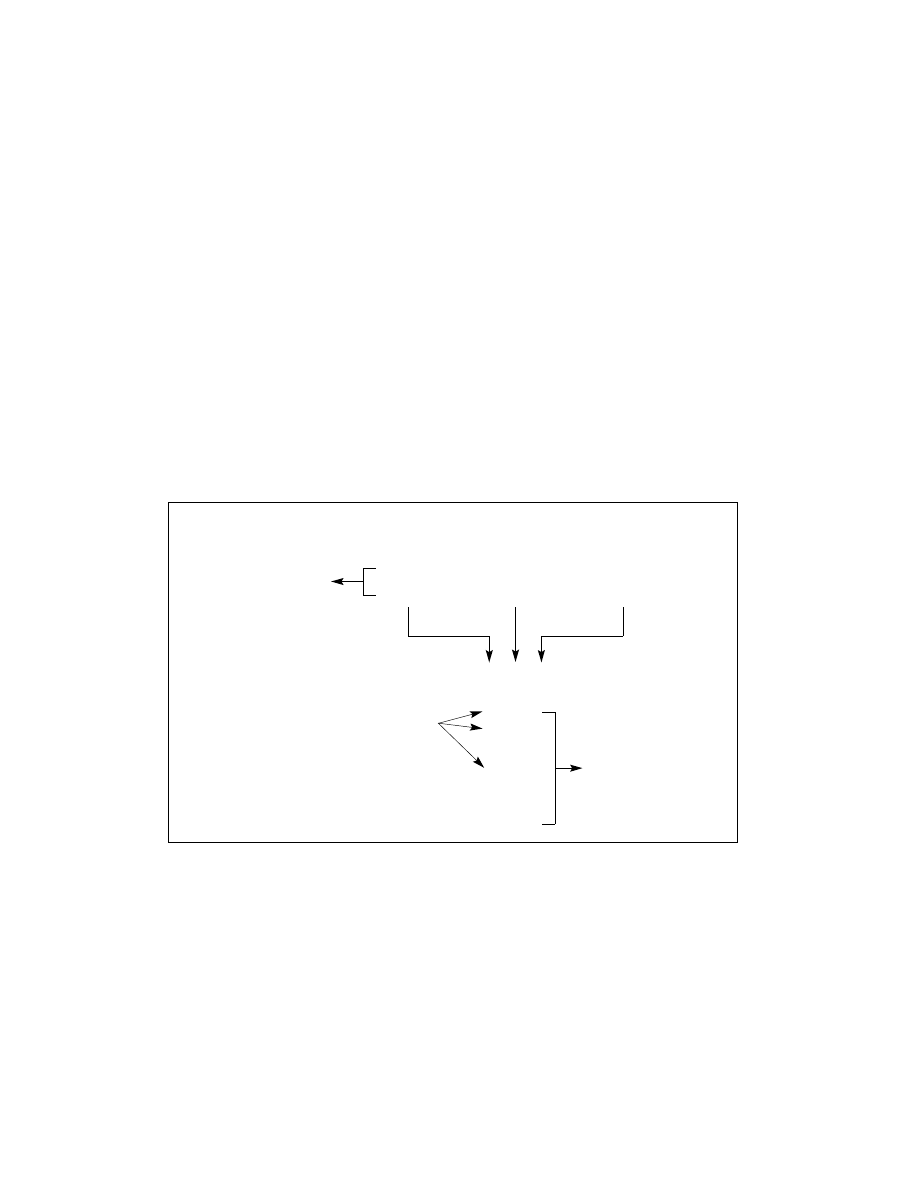

See the example in Figure 8-1. Consider three processors in a system and each processor performs three writes,

one to each of three defined locations (A, B, and C). Individually, the processors perform the writes in the same

program order, but because of bus arbitration and other memory access mechanisms, the order that the three

processors write the individual memory locations can differ each time the respective code sequences are executed

on the processors. The final values in location A, B, and C would possibly vary on each execution of the write

sequence.

The processor-ordering model described in this section is virtually identical to that used by the Pentium and

Intel486 processors. The only enhancements in the Pentium 4, Intel Xeon, and P6 family processors are:

•

Added support for speculative reads, while still adhering to the ordering principles above.

•

Store-buffer forwarding, when a read passes a write to the same memory location.

•

Out of order store from long string store and string move operations (see Section 8.2.4, “Fast-String Operation

and Out-of-Order Stores,” below).

NOTE

In P6 processor family, store-buffer forwarding to reads of WC memory from streaming stores to the same address

does not occur due to errata.

8.2.3

Examples Illustrating the Memory-Ordering Principles

This section provides a set of examples that illustrate the behavior of the memory-ordering principles introduced in

Section 8.2.2. They are designed to give software writers an understanding of how memory ordering may affect

the results of different sequences of instructions.

Figure 8-1. Example of Write Ordering in Multiple-Processor Systems

Processor #1

Processor #2

Processor #3

Write A.3

Write B.3

Write C.3

Write A.1

Write B.1

Write A.2

Write A.3

Write C.1

Write B.2

Write C.2

Write B.3

Write C.3

Order of Writes From Individual Processors

Write A.2

Write B.2

Write C.2

Write A.1

Write B.1

Write C.1

Writes from all

processors are

not guaranteed

to occur in a

particular order.

Each processor

is guaranteed to

perform writes in

program order.

Writes are in order

with respect to

individual processes.

Example of order of actual writes

from all processors to memory