Vol. 3A 7-17

TASK MANAGEMENT

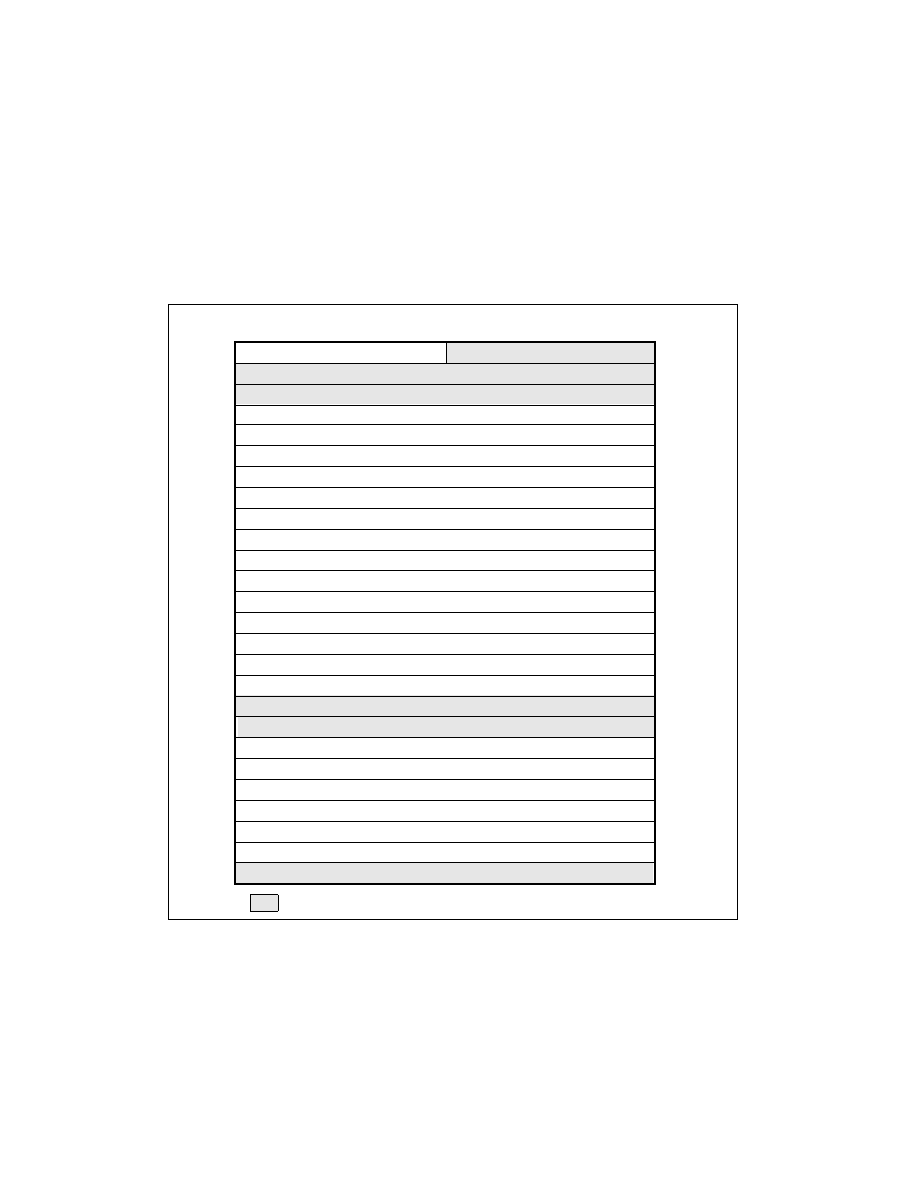

Although hardware task-switching is not supported in 64-bit mode, a 64-bit task state segment (TSS) must exist.

Figure 7-11 shows the format of a 64-bit TSS. The TSS holds information important to 64-bit mode and that is not

directly related to the task-switch mechanism. This information includes:

•

RSPn — The full 64-bit canonical forms of the stack pointers (RSP) for privilege levels 0-2.

•

ISTn — The full 64-bit canonical forms of the interrupt stack table (IST) pointers.

•

I/O map base address — The 16-bit offset to the I/O permission bit map from the 64-bit TSS base.

The operating system must create at least one 64-bit TSS after activating IA-32e mode. It must execute the LTR

instruction (in 64-bit mode) to load the TR register with a pointer to the 64-bit TSS responsible for both 64-bit-

mode programs and compatibility-mode programs.

Figure 7-11. 64-Bit TSS Format

0

31

100

96

92

88

84

80

76

I/O Map Base Address

15

72

68

64

60

56

52

48

44

40

36

32

28

24

20

16

12

8

4

0

RSP0 (lower 32 bits)

RSP1 (lower 32 bits)

RSP2 (lower 32 bits)

Reserved bits. Set to 0.

RSP0 (upper 32 bits)

RSP1 (upper 32 bits)

RSP2 (upper 32 bits)

IST1 (lower 32 bits)

IST1 (upper 32 bits)

IST2 (lower 32 bits)

IST3 (lower 32 bits)

IST4 (lower 32 bits)

IST5 (lower 32 bits)

IST6 (lower 32 bits)

IST7 (lower 32 bits)

IST2 (upper 32 bits)

IST3 (upper 32 bits)

IST4 (upper 32 bits)

IST5 (upper 32 bits)

IST6 (upper 32 bits)

IST7 (upper 32 bits)

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved