Vol. 3A 7-15

TASK MANAGEMENT

7.5.2

Task Logical Address Space

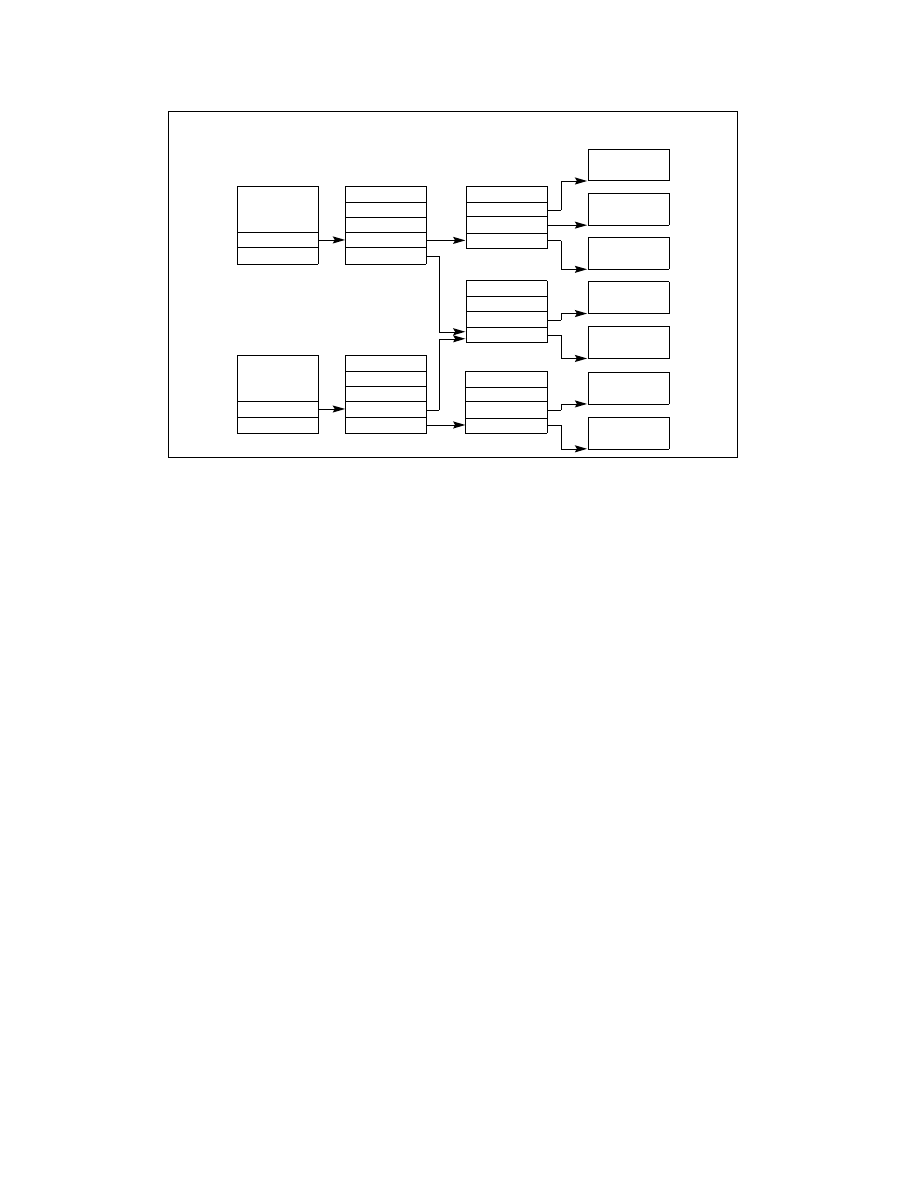

To allow the sharing of data among tasks, use the following techniques to create shared logical-to-physical

address-space mappings for data segments:

•

Through the segment descriptors in the GDT — All tasks must have access to the segment descriptors in

the GDT. If some segment descriptors in the GDT point to segments in the linear-address space that are

mapped into an area of the physical-address space common to all tasks, then all tasks can share the data and

code in those segments.

•

Through a shared LDT — Two or more tasks can use the same LDT if the LDT fields in their TSSs point to the

same LDT. If some segment descriptors in a shared LDT point to segments that are mapped to a common area

of the physical address space, the data and code in those segments can be shared among the tasks that share

the LDT. This method of sharing is more selective than sharing through the GDT, because the sharing can be

limited to specific tasks. Other tasks in the system may have different LDTs that do not give them access to the

shared segments.

•

Through segment descriptors in distinct LDTs that are mapped to common addresses in linear

address space — If this common area of the linear address space is mapped to the same area of the physical

address space for each task, these segment descriptors permit the tasks to share segments. Such segment

descriptors are commonly called aliases. This method of sharing is even more selective than those listed above,

because, other segment descriptors in the LDTs may point to independent linear addresses which are not

shared.

7.6

16-BIT TASK-STATE SEGMENT (TSS)

The 32-bit IA-32 processors also recognize a 16-bit TSS format like the one used in Intel 286 processors (see

Figure 7-10). This format is supported for compatibility with software written to run on earlier IA-32 processors.

The following information is important to know about the 16-bit TSS.

•

Do not use a 16-bit TSS to implement a virtual-8086 task.

•

The valid segment limit for a 16-bit TSS is 2CH.

Figure 7-9. Overlapping Linear-to-Physical Mappings

Task A

TSS

PDE

Page Directories

PDE

PTE

PTE

PTE

PTE

PTE

Page Tables

Page Frames

Task A

Task A

Shared

Shared

Task B

Task B

Shared PT

PTE

PTE

PDE

PDE

PDBR

PDBR

Task A TSS

Task B TSS