7-16 Vol. 3A

TASK MANAGEMENT

•

The 16-bit TSS does not contain a field for the base address of the page directory, which is loaded into control

register CR3. A separate set of page tables for each task is not supported for 16-bit tasks. If a 16-bit task is

dispatched, the page-table structure for the previous task is used.

•

The I/O base address is not included in the 16-bit TSS. None of the functions of the I/O map are supported.

•

When task state is saved in a 16-bit TSS, the upper 16 bits of the EFLAGS register and the EIP register are lost.

•

When the general-purpose registers are loaded or saved from a 16-bit TSS, the upper 16 bits of the registers

are modified and not maintained.

7.7

TASK MANAGEMENT IN 64-BIT MODE

In 64-bit mode, task structure and task state are similar to those in protected mode. However, the task switching

mechanism available in protected mode is not supported in 64-bit mode. Task management and switching must be

performed by software. The processor issues a general-protection exception (#GP) if the following is attempted in

64-bit mode:

•

Control transfer to a TSS or a task gate using JMP, CALL, INTn, or interrupt.

•

An IRET with EFLAGS.NT (nested task) set to 1.

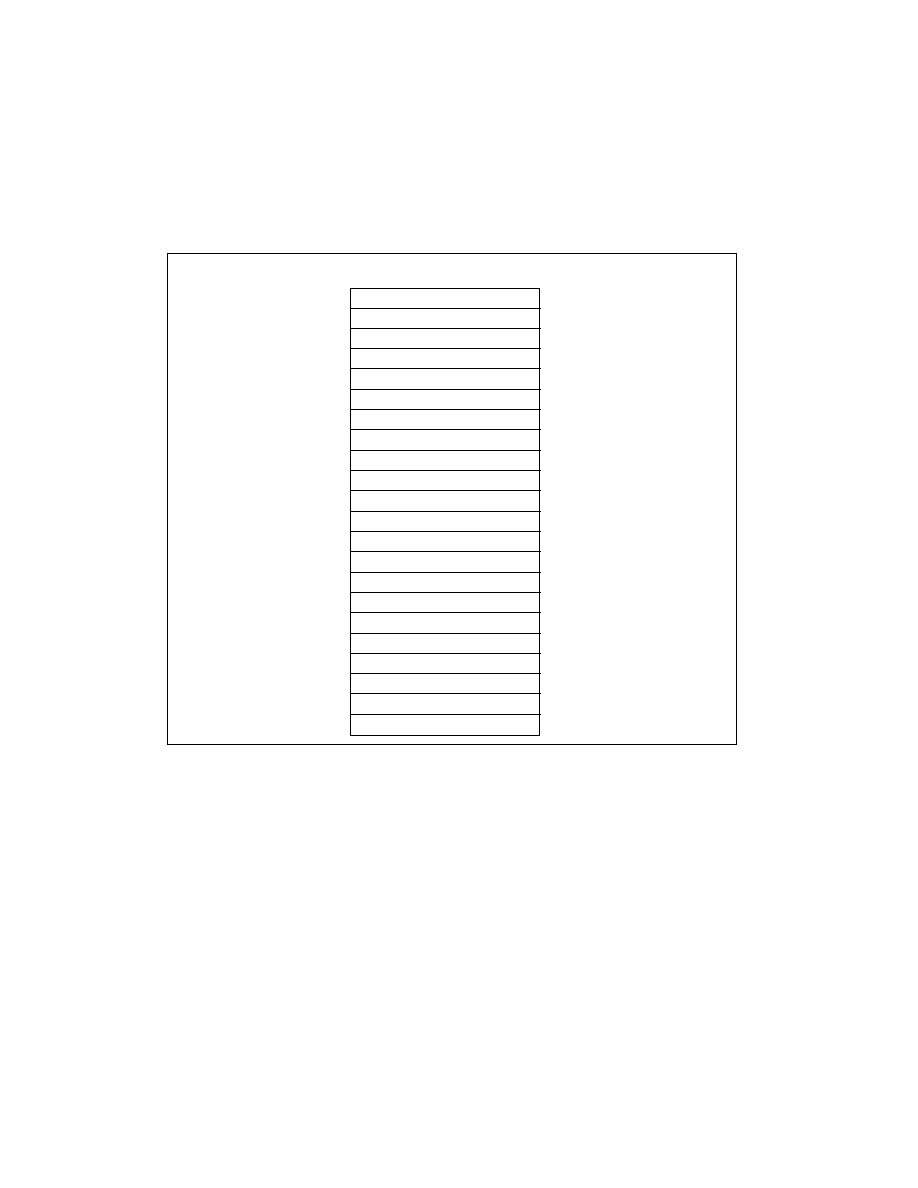

Figure 7-10. 16-Bit TSS Format

Task LDT Selector

DS Selector

SS Selector

CS Selector

ES Selector

DI

SI

BP

SP

BX

DX

CX

AX

FLAG Word

IP (Entry Point)

SS2

SP2

SS1

SP1

SS0

SP0

Previous Task Link

15

0

42

40

36

34

32

30

38

28

26

24

22

20

18

16

14

12

10

8

6

4

2

0