Vol. 3A 7-11

TASK MANAGEMENT

occurs after the commit point (in step 13), the processor completes the task switch (without

performing additional access and segment availability checks) and generates the appropriate

exception prior to beginning execution of the new task.

If exceptions occur after the commit point, the exception handler must finish the task switch itself

before allowing the processor to begin executing the new task. See Chapter 6, “Interrupt

10—Invalid TSS Exception (#TS),” for more information about the affect of exceptions on a task

when they occur after the commit point of a task switch.

14. Begins executing the new task. (To an exception handler, the first instruction of the new task appears not to

have been executed.)

The state of the currently executing task is always saved when a successful task switch occurs. If the task is

resumed, execution starts with the instruction pointed to by the saved EIP value, and the registers are restored to

the values they held when the task was suspended.

When switching tasks, the privilege level of the new task does not inherit its privilege level from the suspended

task. The new task begins executing at the privilege level specified in the CPL field of the CS register, which is

loaded from the TSS. Because tasks are isolated by their separate address spaces and TSSs and because privilege

rules control access to a TSS, software does not need to perform explicit privilege checks on a task switch.

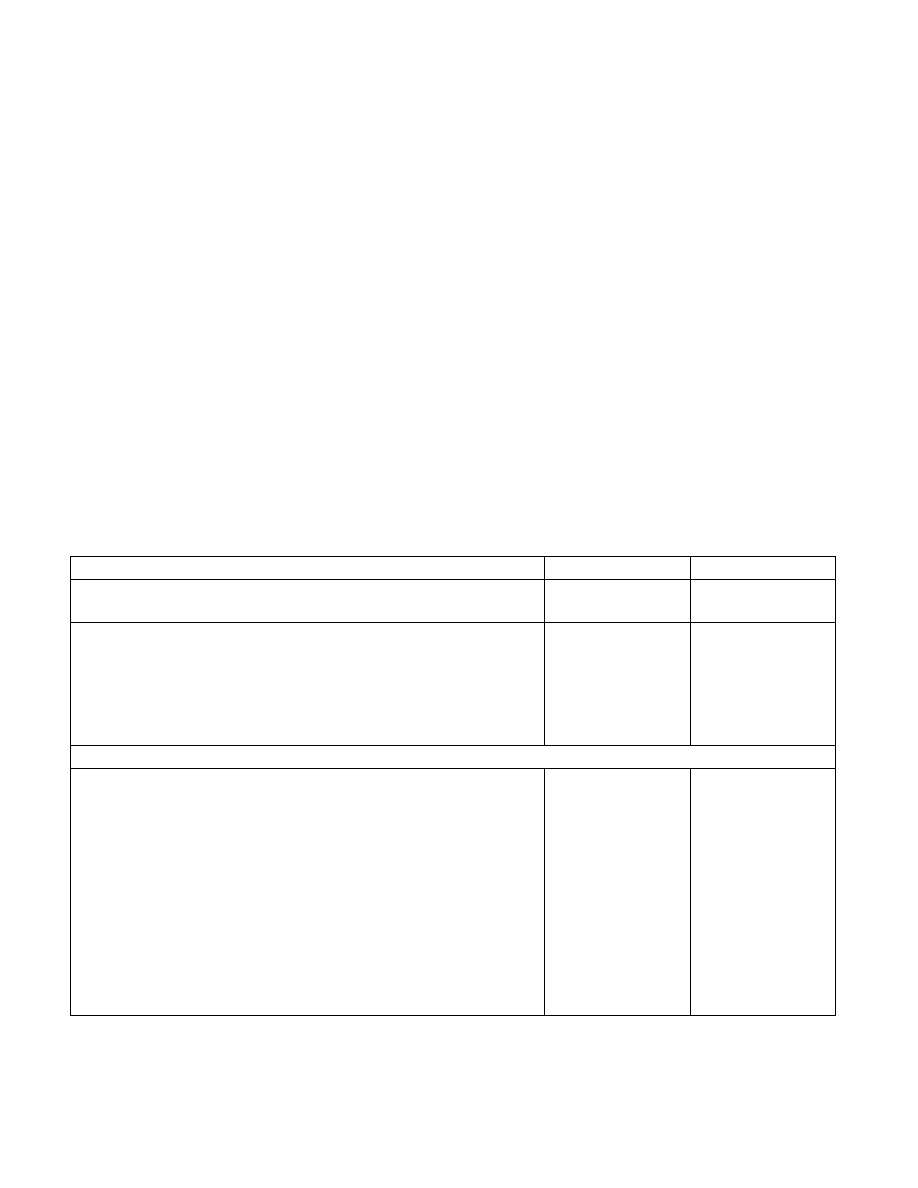

Table 7-1 shows the exception conditions that the processor checks for when switching tasks. It also shows the

exception that is generated for each check if an error is detected and the segment that the error code references.

(The order of the checks in the table is the order used in the P6 family processors. The exact order is model specific

and may be different for other IA-32 processors.) Exception handlers designed to handle these exceptions may be

subject to recursive calls if they attempt to reload the segment selector that generated the exception. The cause of

the exception (or the first of multiple causes) should be fixed before reloading the selector.

Table 7-1. Exception Conditions Checked During a Task Switch

Condition Checked

Exception

1

Error Code Reference

2

Segment selector for a TSS descriptor references

the GDT and is within the limits of the table.

#GP

#TS (for IRET)

New Task’s TSS

TSS descriptor is present in memory.

#NP

New Task’s TSS

TSS descriptor is not busy (for task switch initiated by a call, interrupt, or

exception).

#GP (for JMP, CALL, INT) Task’s back-link TSS

TSS descriptor is not busy (for task switch initiated by an IRET instruction).

#TS (for IRET)

New Task’s TSS

TSS segment limit greater than or equal to 108 (for 32-bit TSS) or 44 (for 16-bit

TSS).

#TS

New Task’s TSS

Registers are loaded from the values in the TSS.

LDT segment selector of new task is valid

3

.

#TS

New Task’s LDT

Code segment DPL matches segment selector RPL.

#TS

New Code Segment

SS segment selector is valid

2

.

#TS

New Stack Segment

Stack segment is present in memory.

#SS

New Stack Segment

Stack segment DPL matches CPL.

#TS

New stack segment

LDT of new task is present in memory.

#TS

New Task’s LDT

CS segment selector is valid

3

.

#TS

New Code Segment

Code segment is present in memory.

#NP

New Code Segment

Stack segment DPL matches selector RPL.

#TS

New Stack Segment

DS, ES, FS, and GS segment selectors are valid

3

.

#TS

New Data Segment

DS, ES, FS, and GS segments are readable.

#TS

New Data Segment