Vol. 3A 7-7

TASK MANAGEMENT

7.2.4 Task

Register

The task register holds the 16-bit segment selector and the entire segment descriptor (32-bit base address (64 bits

in IA-32e mode), 16-bit segment limit, and descriptor attributes) for the TSS of the current task (see Figure 2-6).

This information is copied from the TSS descriptor in the GDT for the current task. Figure 7-5 shows the path the

processor uses to access the TSS (using the information in the task register).

The task register has a visible part (that can be read and changed by software) and an invisible part (maintained

by the processor and is inaccessible by software). The segment selector in the visible portion points to a TSS

descriptor in the GDT. The processor uses the invisible portion of the task register to cache the segment descriptor

for the TSS. Caching these values in a register makes execution of the task more efficient. The LTR (load task

register) and STR (store task register) instructions load and read the visible portion of the task register:

The LTR instruction loads a segment selector (source operand) into the task register that points to a TSS descriptor

in the GDT. It then loads the invisible portion of the task register with information from the TSS descriptor. LTR is a

privileged instruction that may be executed only when the CPL is 0. It’s used during system initialization to put an

initial value in the task register. Afterwards, the contents of the task register are changed implicitly when a task

switch occurs.

The STR (store task register) instruction stores the visible portion of the task register in a general-purpose register

or memory. This instruction can be executed by code running at any privilege level in order to identify the currently

running task. However, it is normally used only by operating system software. (If CR4.UMIP = 1, STR can be

executed only when CPL = 0.)

On power up or reset of the processor, segment selector and base address are set to the default value of 0; the limit

is set to FFFFH.

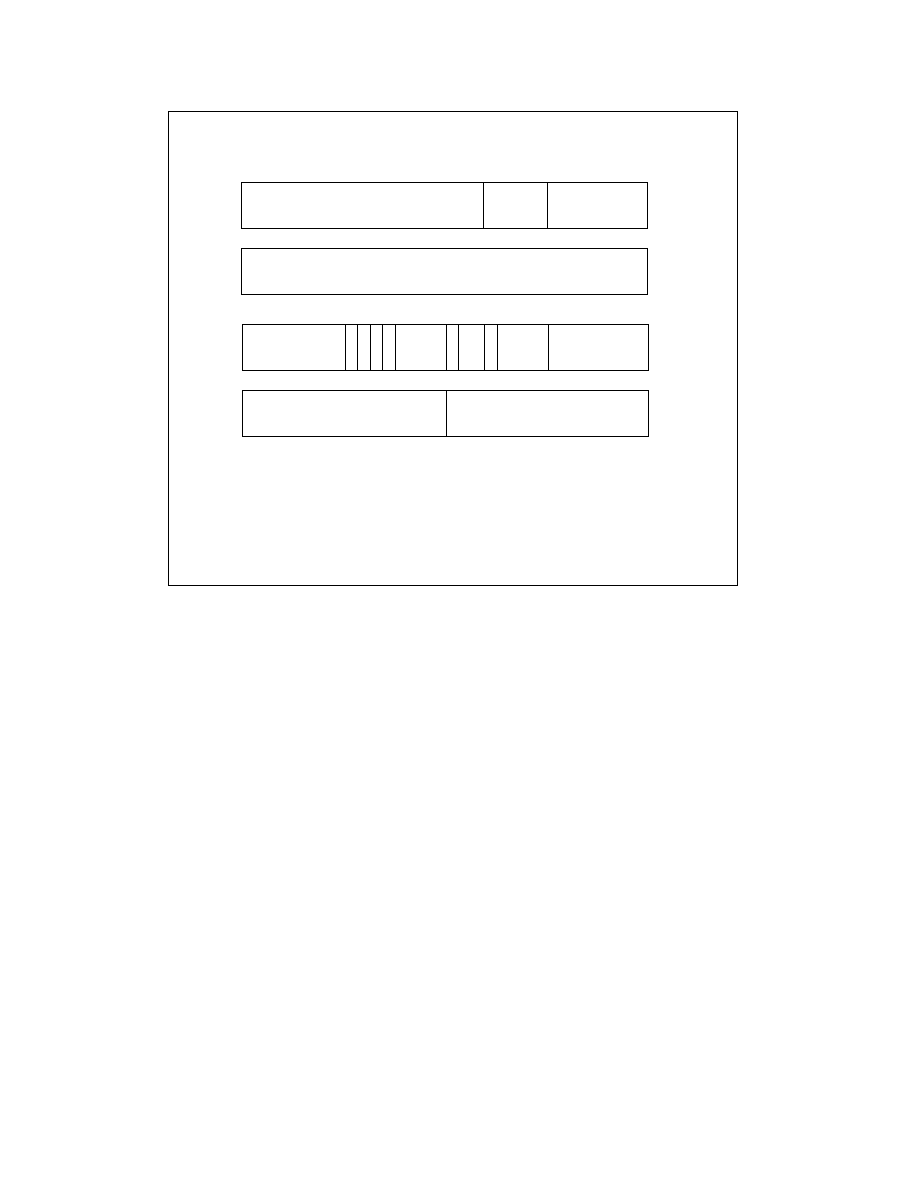

Figure 7-4. Format of TSS and LDT Descriptors in 64-bit Mode

31

24 23 22 21 20 19

16 15

13

14

12 11

8 7

0

P

Base 31:24

G

D

P

L

Type

0

0

31

16 15

0

Base Address 15:00

Segment Limit 15:00

Base 23:16

A

V

L

Limit

19:16

0

TSS (or LDT) Descriptor

AVL

B

BASE

DPL

G

Available for use by system software

Busy flag

Segment Base Address

Descriptor Privilege Level

Granularity

LIMIT

P

TYPE

Segment Limit

Segment Present

Segment Type

0

4

31

13 12

8 7

0

Reserved

31

0

Base Address 63:32

Reserved

0

8

12