Vol. 3A 6-45

INTERRUPT AND EXCEPTION HANDLING

Interrupt 17—Alignment Check Exception (#AC)

Exception Class

Fault.

Description

Indicates that the processor detected an unaligned memory operand when alignment checking was enabled. Align-

ment checks are only carried out in data (or stack) accesses (not in code fetches or system segment accesses). An

example of an alignment-check violation is a word stored at an odd byte address, or a doubleword stored at an

address that is not an integer multiple of 4. Table 6-7 lists the alignment requirements various data types recog-

nized by the processor.

Note that the alignment check exception (#AC) is generated only for data types that must be aligned on word,

doubleword, and quadword boundaries. A general-protection exception (#GP) is generated 128-bit data types that

are not aligned on a 16-byte boundary.

To enable alignment checking, the following conditions must be true:

•

AM flag in CR0 register is set.

•

AC flag in the EFLAGS register is set.

•

The CPL is 3 (protected mode or virtual-8086 mode).

Alignment-check exceptions (#AC) are generated only when operating at privilege level 3 (user mode). Memory

references that default to privilege level 0, such as segment descriptor loads, do not generate alignment-check

exceptions, even when caused by a memory reference made from privilege level 3.

Storing the contents of the GDTR, IDTR, LDTR, or task register in memory while at privilege level 3 can generate

an alignment-check exception. Although application programs do not normally store these registers, the fault can

be avoided by aligning the information stored on an even word-address.

The FXSAVE/XSAVE and FXRSTOR/XRSTOR instructions save and restore a 512-byte data structure, the first byte

of which must be aligned on a 16-byte boundary. If the alignment-check exception (#AC) is enabled when

executing these instructions (and CPL is 3), a misaligned memory operand can cause either an alignment-check

exception or a general-protection exception (#GP) depending on the processor implementation (see “FXSAVE-

Save x87 FPU, MMX, SSE, and SSE2 State” and “FXRSTOR-Restore x87 FPU, MMX, SSE, and SSE2 State” in

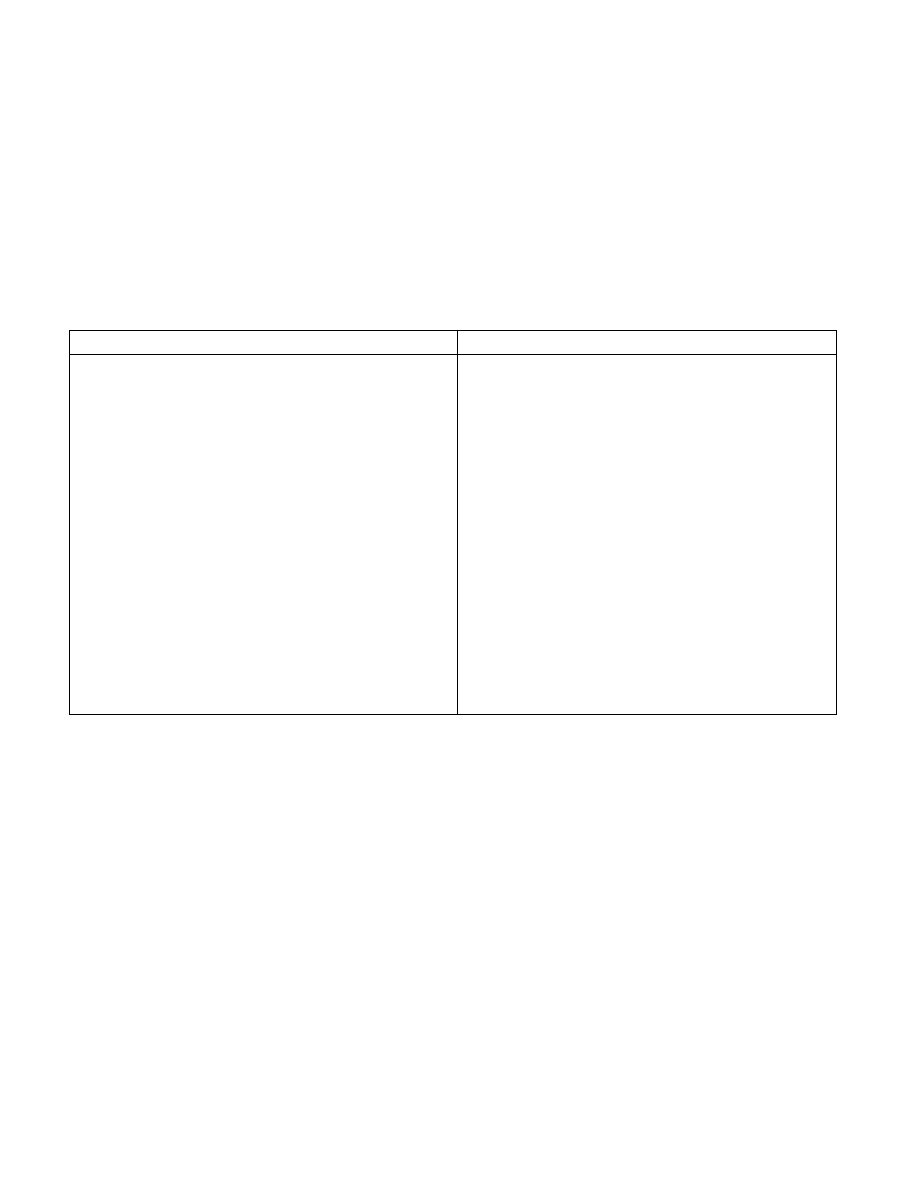

Table 6-7. Alignment Requirements by Data Type

Data Type

Address Must Be Divisible By

Word

2

Doubleword

4

Single-precision floating-point (32-bits)

4

Double-precision floating-point (64-bits)

8

Double extended-precision floating-point (80-bits)

8

Quadword

8

Double quadword

16

Segment Selector

2

32-bit Far Pointer

2

48-bit Far Pointer

4

32-bit Pointer

4

GDTR, IDTR, LDTR, or Task Register Contents

4

FSTENV/FLDENV Save Area

4 or 2, depending on operand size

FSAVE/FRSTOR Save Area

4 or 2, depending on operand size

Bit String

2 or 4 depending on the operand-size attribute.