Vol. 3A 6-41

INTERRUPT AND EXCEPTION HANDLING

— I/D flag (bit 4).

This flag is 1 if the access causing the page-fault exception was an instruction fetch. This flag describes the

access causing the page-fault exception, not the access rights specified by paging.

— PK flag (bit 5).

This flag is 1 if the access causing the page-fault exception was a data access to a user-mode address with

protection key disallowed by the value of the PKRU register.

— SGX flag (bit 15).

This flag is 1 if the exception is unrelated to paging and resulted from violation of SGX-specific access-

control requirements. Because such a violation can occur only if there is no ordinary page fault, this flag is

set only if the P flag (bit 0) is 1 and the RSVD flag (bit 3) and the PK flag (bit 5) are both 0.

See Section 4.6, “Access Rights” and Section 4.7, “Page-Fault Exceptions” for more information about page-

fault exceptions and the error codes that they produce.

•

The contents of the CR2 register. The processor loads the CR2 register with the 32-bit linear address that

generated the exception. The page-fault handler can use this address to locate the corresponding page

directory and page-table entries. Another page fault can potentially occur during execution of the page-fault

handler; the handler should save the contents of the CR2 register before a second page fault can occur.

1

If a

page fault is caused by a page-level protection violation, the access flag in the page-directory entry is set when

the fault occurs. The behavior of IA-32 processors regarding the access flag in the corresponding page-table

entry is model specific and not architecturally defined.

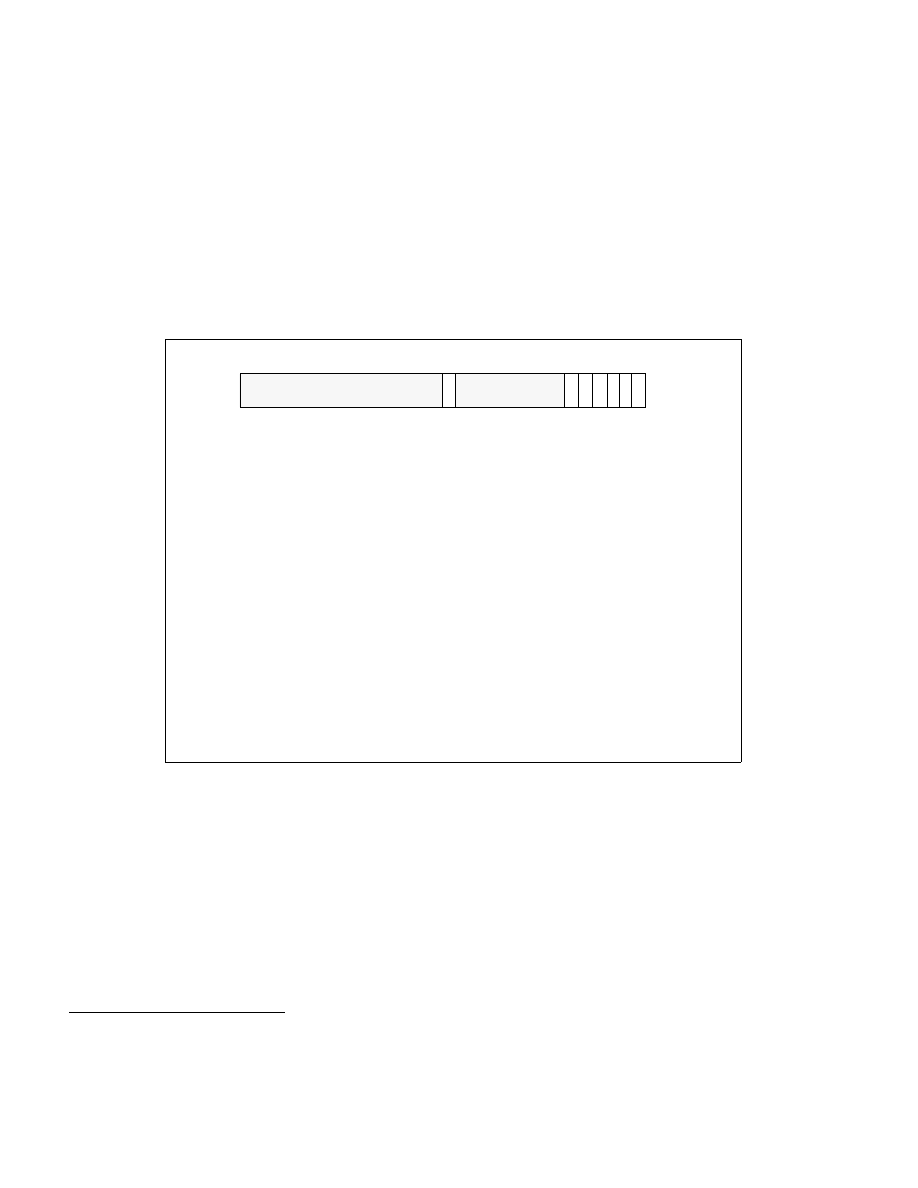

Figure 6-9. Page-Fault Error Code

1. Processors update CR2 whenever a page fault is detected. If a second page fault occurs while an earlier page fault is being deliv-

ered, the faulting linear address of the second fault will overwrite the contents of CR2 (replacing the previous address). These

updates to CR2 occur even if the page fault results in a double fault or occurs during the delivery of a double fault.

The fault was caused by a non-present page.

The fault was caused by a page-level protection violation.

The access causing the fault was a read.

The access causing the fault was a write.

A supervisor-mode access caused the fault.

A user-mode access caused the fault.

31

0

Reserved

1

2

3

4

The fault was not caused by reserved bit violation.

The fault was caused by a reserved bit set to 1 in some

P

0

1

W/R

0

1

U/S

0

RSVD

0

1

1

I/D

I/D

0 The fault was not caused by an instruction fetch.

1 The fault was caused by an instruction fetch.

P

W/R

U/S

RSVD

paging-structure entry.

PK 5

PK

0 The fault was not caused by protection keys.

1 There was a protection-key violation.

SGX

The fault is not related to SGX.

0

1 The fault resulted from violation of SGX-specific access-control

requirements.

Reserved

SG

X

15