Vol. 3A 6-15

INTERRUPT AND EXCEPTION HANDLING

NOTE

Because IA-32 architecture tasks are not re-entrant, an interrupt-handler task must disable

interrupts between the time it completes handling the interrupt and the time it executes the IRET

instruction. This action prevents another interrupt from occurring while the interrupt task’s TSS is

still marked busy, which would cause a general-protection (#GP) exception.

6.13 ERROR

CODE

When an exception condition is related to a specific segment selector or IDT vector, the processor pushes an error

code onto the stack of the exception handler (whether it is a procedure or task). The error code has the format

shown in Figure 6-6. The error code resembles a segment selector; however, instead of a TI flag and RPL field, the

error code contains 3 flags:

EXT

External event (bit 0) — When set, indicates that the exception occurred during delivery of an

event external to the program, such as an interrupt or an earlier exception.

IDT

Descriptor location (bit 1) — When set, indicates that the index portion of the error code refers

to a gate descriptor in the IDT; when clear, indicates that the index refers to a descriptor in the GDT

or the current LDT.

TI

GDT/LDT (bit 2) — Only used when the IDT flag is clear. When set, the TI flag indicates that the

index portion of the error code refers to a segment or gate descriptor in the LDT; when clear, it indi-

cates that the index refers to a descriptor in the current GDT.

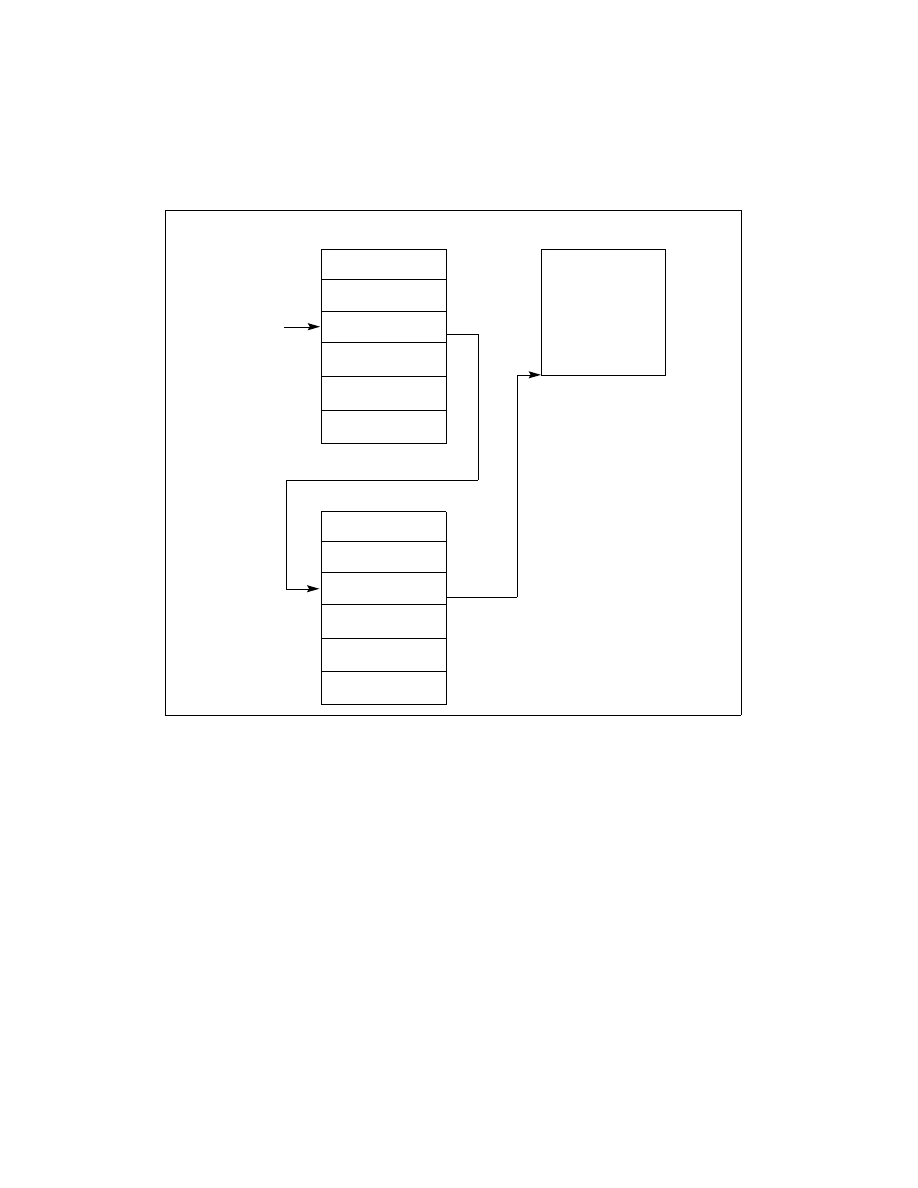

Figure 6-5. Interrupt Task Switch

IDT

Task Gate

TSS for Interrupt-

TSS Selector

GDT

TSS Descriptor

Interrupt

Vector

TSS

Base

Address

Handling Task