Vol. 3A 6-11

INTERRUPT AND EXCEPTION HANDLING

6.12

EXCEPTION AND INTERRUPT HANDLING

The processor handles calls to exception- and interrupt-handlers similar to the way it handles calls with a CALL

instruction to a procedure or a task. When responding to an exception or interrupt, the processor uses the excep-

tion or interrupt vector as an index to a descriptor in the IDT. If the index points to an interrupt gate or trap gate,

the processor calls the exception or interrupt handler in a manner similar to a CALL to a call gate (see Section

5.8.2, “Gate Descriptors,” through Section 5.8.6, “Returning from a Called Procedure”). If index points to a task

gate, the processor executes a task switch to the exception- or interrupt-handler task in a manner similar to a CALL

to a task gate (see Section 7.3, “Task Switching”).

6.12.1

Exception- or Interrupt-Handler Procedures

An interrupt gate or trap gate references an exception- or interrupt-handler procedure that runs in the context of

the currently executing task (see Figure 6-3). The segment selector for the gate points to a segment descriptor for

an executable code segment in either the GDT or the current LDT. The offset field of the gate descriptor points to

the beginning of the exception- or interrupt-handling procedure.

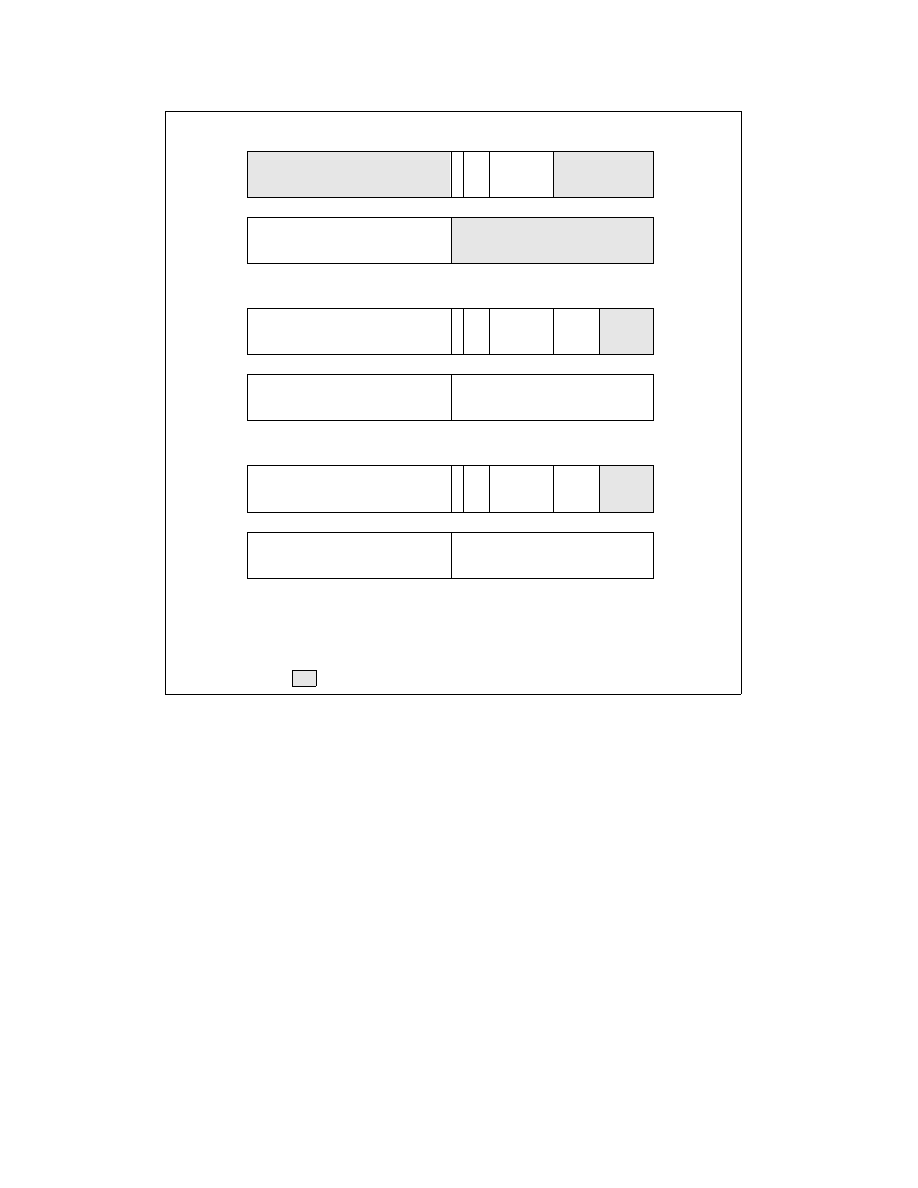

Figure 6-2. IDT Gate Descriptors

31

16 15

13

14

12

8 7

0

P

Offset 31..16

D

P

L

0

4

31

16 15

0

Segment Selector

Offset 15..0

0

0

1

1

D

Interrupt Gate

DPL

Offset

P

Selector

Descriptor Privilege Level

Offset to procedure entry point

Segment Present flag

Segment Selector for destination code segment

31

16 15

13

14

12

8 7

0

P

D

P

L

0

4

31

16 15

0

TSS Segment Selector

0

1

0

1

0

Task Gate

4

5

0 0 0

31

16 15

13

14

12

8 7

0

P

Offset 31..16

D

P

L

0

4

31

16 15

0

Segment Selector

Offset 15..0

0

1

1

1

D

Trap Gate

4

5

0 0 0

Reserved

Size of gate: 1 = 32 bits; 0 = 16 bits

D