B-8 Vol. 3D

FIELD ENCODING IN VMCS

The limit fields for GDTR and IDTR are defined to be 32 bits in width even though these fields are only 16-bits wide

in the Intel 64 and IA-32 architectures. VM entry ensures that the high 16 bits of both these fields are cleared to 0.

B.3.4

32-Bit Host-State Field

A value of 3 in bits 11:10 of an encoding indicates a field in the host-state area. There is only one such 32-bit field

as given in Table B-11.

B.4 NATURAL-WIDTH

FIELDS

A value of 3 in bits 14:13 of an encoding indicates a natural-width field. As noted in Section 24.11.2, each of these

fields allows only full access, meaning that bit 0 of its encoding is 0. Each such encoding is thus an even number.

B.4.1

Natural-Width Control Fields

A value of 0 in bits 11:10 of an encoding indicates a control field. These fields are distinguished by their index value

in bits 9:1. Table B-12 enumerates the natural-width control fields.

Guest SMBASE

000010100B

00004828H

Guest IA32_SYSENTER_CS

000010101B

0000482AH

VMX-preemption timer value

1

000010111B

0000482EH

NOTES:

1. This field exists only on processors that support the 1-setting of the "activate VMX-preemption timer" VM-execution control.

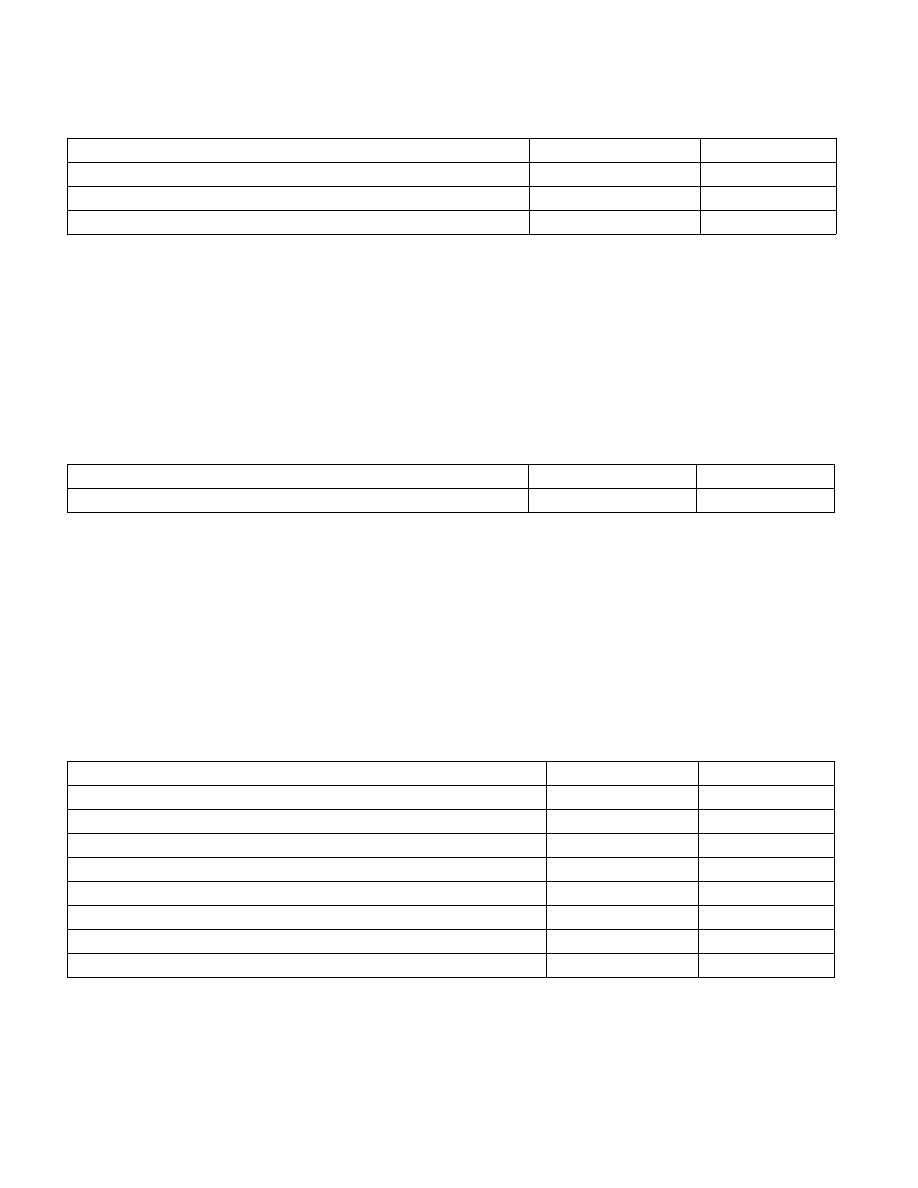

Table B-11. Encoding for 32-Bit Host-State Field (0100_11xx_xxxx_xxx0B)

Field Name

Index

Encoding

Host IA32_SYSENTER_CS

000000000B

00004C00H

Table B-12. Encodings for Natural-Width Control Fields (0110_00xx_xxxx_xxx0B)

Field Name

Index

Encoding

CR0 guest/host mask

000000000B

00006000H

CR4 guest/host mask

000000001B

00006002H

CR0 read shadow

000000010B

00006004H

CR4 read shadow

000000011B

00006006H

CR3-target value 0

000000100B

00006008H

CR3-target value 1

000000101B

0000600AH

CR3-target value 2

000000110B

0000600CH

CR3-target value 3

1

NOTES:

1. If a future implementation supports more than 4 CR3-target values, they will be encoded consecutively following the 4 encodings

given here.

000000111B

0000600EH

Table B-10. Encodings for 32-Bit Guest-State Fields

(0100_10xx_xxxx_xxx0B) (Contd.)

Field Name

Index

Encoding