Vol. 3D 41-3

SGX INSTRUCTION REFERENCES

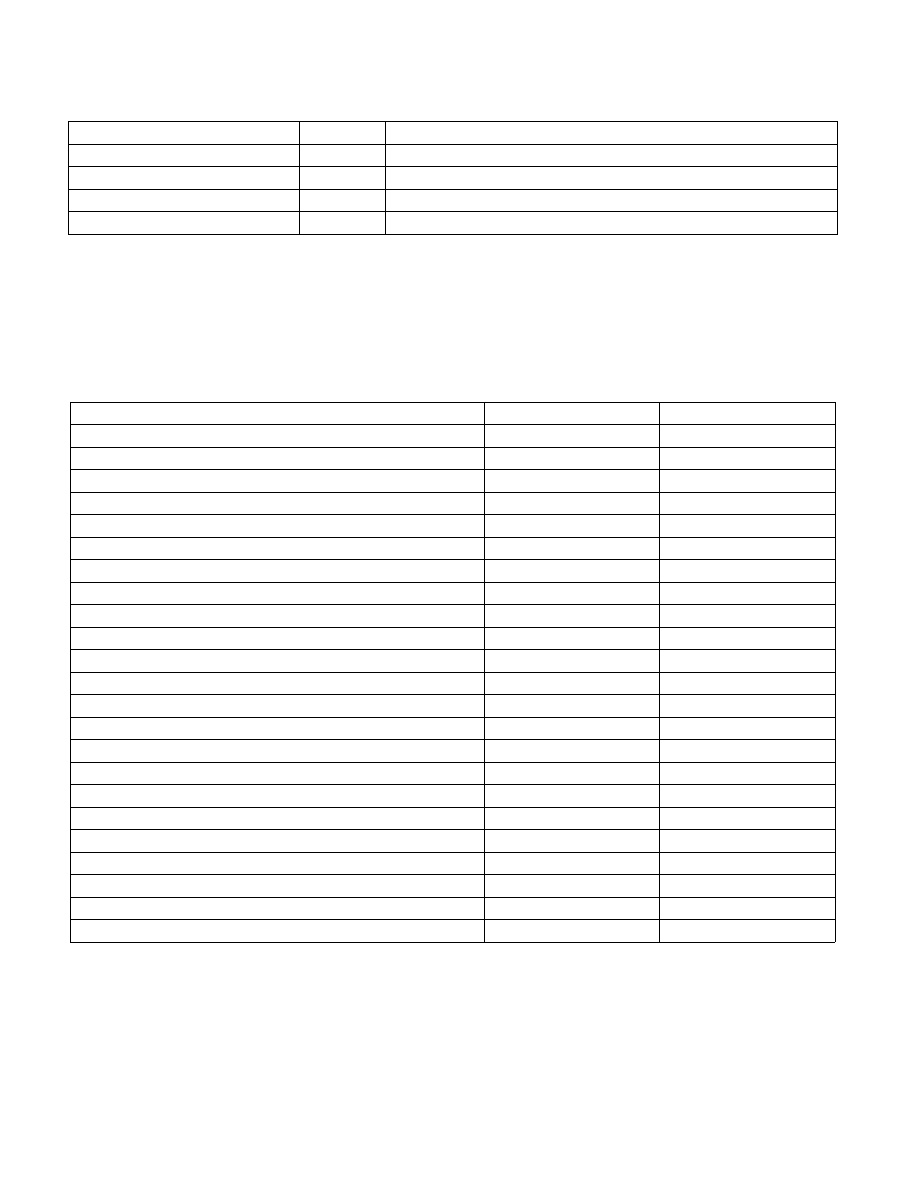

41.1.4 Internal

CREGs

The CREGs as shown in Table 5-4 are hardware specific registers used in this document to indicate values kept by

the processor. These values are used while executing in enclave mode or while executing an Intel SGX instruction.

These registers are not software visible and are implementation specific. The values in Table 41-4 appear at various

places in the pseudo-code of this document. They are used to enhance understanding of the operations.

41.1.5

Concurrent Operation Restrictions

To protect the integrity of Intel SGX data structures, under certain conditions, Intel SGX disallows certain leaf func-

tions from operating concurrently. Listed below are some examples of concurrency that are not allowed.

•

For example, Intel SGX disallows the following leafs to concurrently operate on the same EPC page.

SGX_INVALID_CPUSVN

32

EINIT, EGETKEY

SGX_INVALID_ISVSVN

64

EGETKEY

SGX_UNMASKED_EVENT

128

EINIT

SGX_INVALID_KEYNAME

256

EGETKEY

Table 41-4. List of Internal CREG

Name

Size (Bits)

Scope

CR_ENCLAVE_MODE

1

LP

CR_DBGOPTIN

1

LP

CR_TCS_LA

64

LP

CR_TCS_PH

64

LP

CR_ACTIVE_SECS

64

LP

CR_ELRANGE

128

LP

CR_SAVE_TF

1

LP

CR_SAVE_FS

64

LP

CR_GPR_PA

64

LP

CR_XSAVE_PAGE_n

64

LP

CR_SAVE_DR7

64

LP

CR_SAVE_PERF_GLOBAL_CTRL

64

LP

CR_SAVE_DEBUGCTL

64

LP

CR_SAVE_PEBS_ENABLE

64

LP

CR_CPUSVN

128

PACKAGE

CSR_SGX_OWNEREPOCH

128

PACKAGE

CR_SAVE_XCR0

64

LP

CR_SGX_ATTRIBUTES_MASK

128

LP

CR_PAGING_VERSION

64

PACKAGE

CR_VERSION_THRESHOLD

64

PACKAGE

CR_NEXT_EID

64

PACKAGE

CR_BASE_PK

128

PACKAGE

CR_SEAL_FUSES

128

PACKAGE

Table 41-3. Error or Information Codes for Intel® SGX Instructions

Name

Value

Returned By