Vol. 3D 40-3

ENCLAVE EXITING EVENTS

tion from within the enclave. A subsequent ERESUME restores the processor state from the current SSA frame and

frees the SSA frame.

The format of the XSAVE section of SSA is identical to the format used by the XSAVE/XRSTOR instructions. On

EENTER, CSSA must be less than NSSA, ensuring that there is at least one State Save Area slot available for exits.

If there is no free SSA frame when executing EENTER, the entry will fail.

40.3

SYNTHETIC STATE ON ASYNCHRONOUS ENCLAVE EXIT

40.3.1

Processor Synthetic State on Asynchronous Enclave Exit

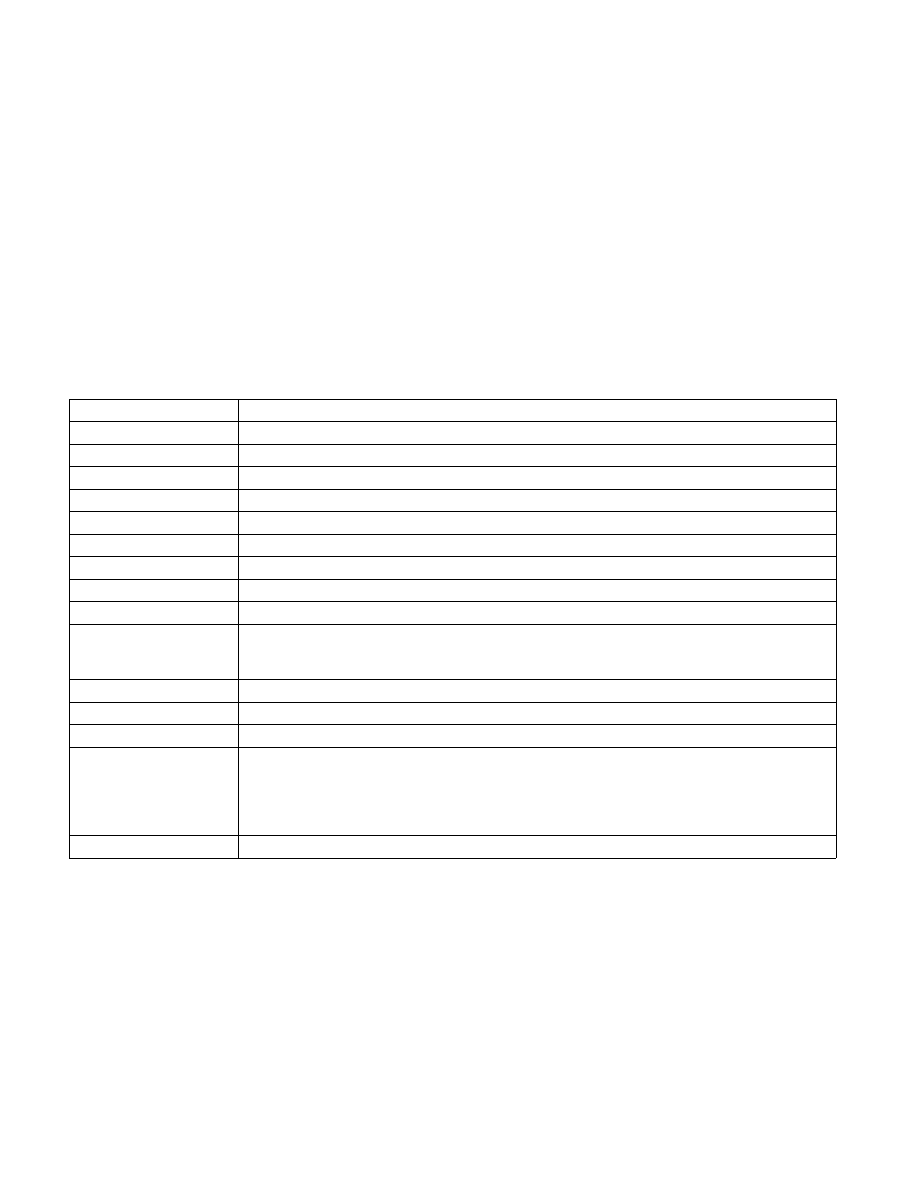

Table 40-1 shows the synthetic state loaded on AEX. The values shown are the lower 32 bits when the processor is

in 32 bit mode and 64 bits when the processor is in 64 bit mode.

40.3.2

Synthetic State for Extended Features

When CR4.OSXSAVE = 1, extended features (those controlled by XCR0[63:2]) are set to their respective INIT

states when this corresponding bit of SECS.XFRM is set. The INIT state is the state that would be loaded by the

XRSTOR instruction had the instruction mask and the XSTATE_BV field of the XSAVE header each contained the

value XFRM. (When the AEX occurs in 32-bit mode, those features that do not exist in 32-bit mode are unchanged.)

Table 40-1. GPR, x87 Synthetic States on Asynchronous Enclave Exit

Register

Value

RAX

3 (ENCLU[3] is ERESUME).

RBX

Pointer to TCS of interrupted enclave thread.

RCX

AEP of interrupted enclave thread.

RDX, RSI, RDI

0.

RSP

Restored from SSA.uRSP.

RBP

Restored from SSA.uRBP.

R8-R15

0 in 64-bit mode; unchanged in 32-bit mode.

RIP

AEP of interrupted enclave thread.

RFLAGS

CF, PF, AF, ZF, SF, OF, RF bits are cleared. All other bits are left unchanged.

x87/SSE State

Unless otherwise listed here, all x87 and SSE state are set to the INIT state. The INIT state is the state

that would be loaded by the XRSTOR instruction with bits 1:0 both set in the requested feature bitmask

(RFBM), and both clear in XSTATE_BV the XSAVE header.

FCW

On #MF exception: set to 037EH. On all other exits: set to 037FH.

FSW

On #MF exception: set to 8081H. On all other exits: set to 0H.

MXCSR

On #XM exception: set to 1F01H. On all other exits: set to 1FB0H.

CR2

If the event that caused the AEX is a #PF, and the #PF does not directly cause a VM exit, then the low

12 bits are cleared.

If the #PF leads directly to a VM exit, CR2 is not updated (usual IA behavior).

Note: The low 12 bits are not cleared if a #PF is encountered during the delivery of the EEE that caused

the AEX. This is because the #PF was not the EEE.

FS, GS

Restored to values as of most recent EENTER/ERESUME.