36-78 Vol. 3C

INTEL® PROCESSOR TRACE

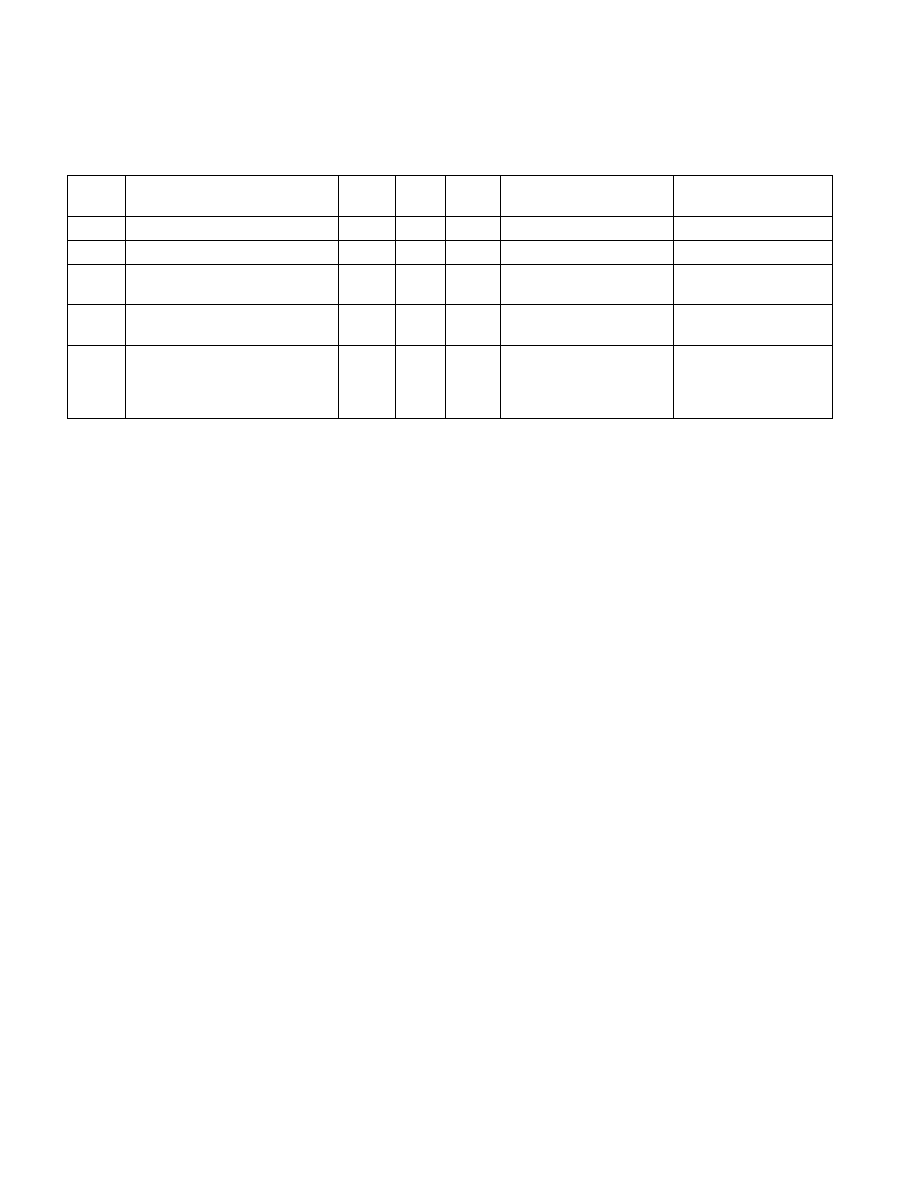

In Table 36-52, PktEn is evaluated based on (TiggerEn & ContextEn & FilterEn & BranchEn & PTWEn).

36.8 SOFTWARE

CONSIDERATIONS

36.8.1

Tracing SMM Code

Nothing prevents an SMM handler from configuring and enabling packet generation for its own use. As described in

Section , SMI will always clear TraceEn, so the SMM handler would have to set TraceEn in order to enable tracing.

There are some unique aspects and guidelines involved with tracing SMM code, which follows:

1. SMM should save away the existing values of any configuration MSRs that SMM intends to modify for tracing.

This will allow the non-SMM tracing context to be restored before RSM.

2. It is recommended that SMM wait until it sets CSbase to 0 before enabling packet generation, to avoid possible

LIP vs RIP confusion.

3. Packet output cannot be directed to SMRR memory, even while tracing in SMM.

4. Before performing RSM, SMM should take care to restore modified configuration MSRs to the values they had

immediately after #SMI. This involves first disabling packet generation by clearing TraceEn, then restoring any

other configuration MSRs that were modified.

5. RSM

— Software must ensure that TraceEn=0 at the time of RSM. Tracing RSM is not a supported usage model, and

the packets generated by RSM are undefined.

— For processors on which Intel PT and LBR use are mutually exclusive (see Section 36.3.1.2), any RSM

during which TraceEn is restored to 1 will suspend any LBR or BTS logging.

36.8.2

Cooperative Transition of Multiple Trace Collection Agents

A third-party trace-collection tool should take into consideration the fact that it may be deployed on a processor

that supports Intel PT but may run under any operating system.

In such a deployment scenario, Intel recommends that tool agents follow similar principles of cooperative transition

of single-use hardware resources, similar to how performance monitoring tools handle performance monitoring

hardware:

•

Respect the “in-use” ownership of an agent who already configured the trace configuration MSRs, see architec-

tural MSRs with the prefix “IA32_RTIT_” in Chapter 35, “Model-Specific Registers (MSRs)”, where “in-use” can

be determined by reading the “enable bits” in the configuration MSRs.

Table 36-52. PwrEvtEn and PTWEn Packet Generation under Different Enable Conditions

Case

Operation

PktEn

Before

PktEn

After

CntxEn

After

Other Dependencies

Packets Output

16.24a

PTWRITE rm32/64, no fault

dc

dc

dc

None

16.24b

PTWRITE rm32/64, no fault

dc

0

0

None

16.24d

PTWRITE rm32, no fault

dc

1

1

* FUP, IP=1 if FUPonPTW=1 PTW(IP=1?, 4B,

rm32_value), FUP(CLIP)?

16.24e

PTWRITE rm64, no fault

dc

1

1

* FUP, IP=1 if FUPonPTW=1 PTW(IP=1?, 8B,

rm64_value), FUP(CLIP)?

16.25a

PTWRITE mem32/64, fault

dc

dc

dc

See “Exception/fault”

(cases 13[a-z] in Table

36-50) for BranchEn

packets.