36-60 Vol. 3C

INTEL® PROCESSOR TRACE

36.4.2.24 Power Entry (PWRE) Packet

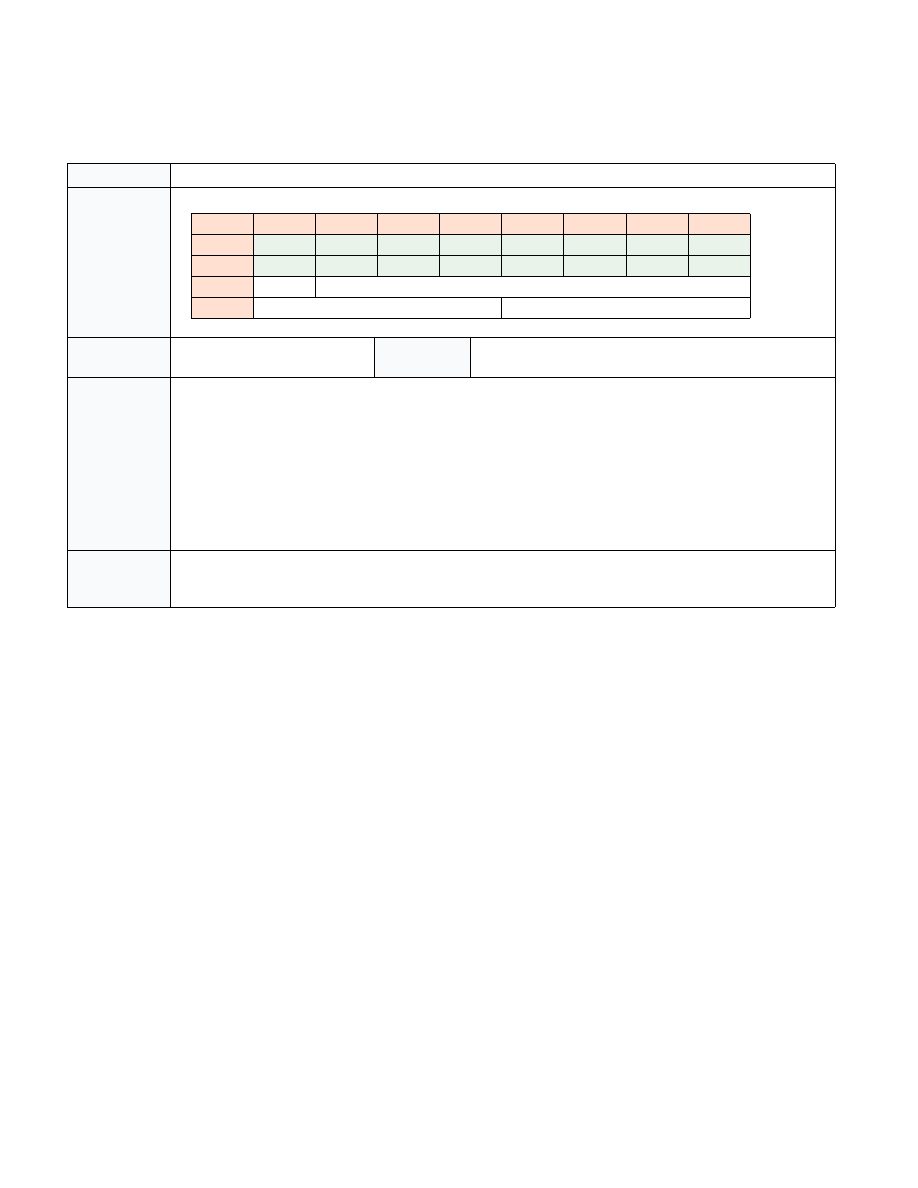

Table 36-43. PWRE Packet Definition

Name

PWRE Packet

Packet Format

Dependencies

TriggerEn & PwrEvtEn

Generation

Scenario

Transition to a C-state deeper than C0.0.

Description

Indicates processor entry to the resolved thread C-state and sub C-state indicated. The processor will remain in this

C-state until either another PWRE indicates the processor has moved to a C-state deeper than C0.0, or a PWRX

packet indicates a return to C0.

Note that some CPUs may allow MWAIT to request a deeper C-state than is supported by the core. These deeper C-

states may have platform-level implications that differentiate them. However, the PWRE packet will provide only

the resolved thread C-state, which will not exceed that supported by the core.

If the C-state entry was initiated by hardware, rather than a direct software request (such as MWAIT, HLT, or shut-

down), the HW bit will be set to indicate this. Hardware Duty Cycling (see Section 14.5, “Hardware Duty Cycling

(HDC)” in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3B) is an example of such a

case.

Application

When transitioning from C0.0 to a deeper C-state, the PWRE packet will be followed by an EXSTOP. If that EXSTOP

packet has the IP bit set, then the following FUP will provide the IP at which the C-state entry occurred. Subsequent

PWRE packets generated before the next PWRX should bind to the same IP.

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

2

HW

Reserved

3

Resolved Thread C-State

Resolved Thread Sub C-State