36-32 Vol. 3C

INTEL® PROCESSOR TRACE

36.3.6.1 Cycle Counter

The cycle counter is implemented in hardware (independent of the time stamp counter or performance monitoring

counters), and is a simple incrementing counter that does not saturate, but rather wraps. The size of the counter is

implementation specific.

The cycle counter is reset to zero any time that TriggerEn is cleared, and when a CYC packet is sent. The cycle

counter will continue to count when ContextEn or FilterEn are cleared, and cycle packets will still be generated. It

will not count during sleep states that result in Intel PT logic being powered-down, but will count up to the point

where clocks are disabled, and resume counting once they are re-enabled.

36.3.6.2 Cycle Packet Semantics

Cycle-accurate mode adheres to the following protocol:

•

All packets that precede a CYC packet represent instructions or events that took place before the CYC time.

•

All packets that follow a CYC packet represent instructions or events that took place at the same time as, or

after, the CYC time.

•

The CYC-eligible packet that immediately follows a CYC packet represents an instruction or event that took

place at the same time as the CYC time.

These items above give the decoder a means to apply CYC packets to a specific instruction in the assembly stream.

Most packets represent a single instruction or event, and hence the CYC packet that precedes each of those packets

represents the retirement time of that instruction or event. In the case of TNT packets, up to 6 conditional branches

and/or compressed RETs may be contained in the packet. In this case, the preceding CYC packet provides the

retirement time of the first branch in the packet. It is possible that multiple branches retired in the same cycle as

that first branch in the TNT, but the protocol will not make that obvious. Also note that a MTC packet could be

generated in the same cycle as the first JCC in the TNT packet. In this case, the CYC would precede both the MTC

and the TNT, and apply to both.

Note that there are times when the cycle counter will stop counting, though cycle-accurate mode is enabled. After

any such scenario, a CYC packet followed by TSC packet will be sent. See Section 36.8.3.2 to understand how to

interpret the payload values

Multi-packet Instructions or Events

Some operations, such as interrupts or task switches, generate multiple packets. In these cases, multiple CYC

packets may be sent for the operation, preceding each CYC-eligible packet in the operation. An example, using a

task switch on a software interrupt, is shown below.

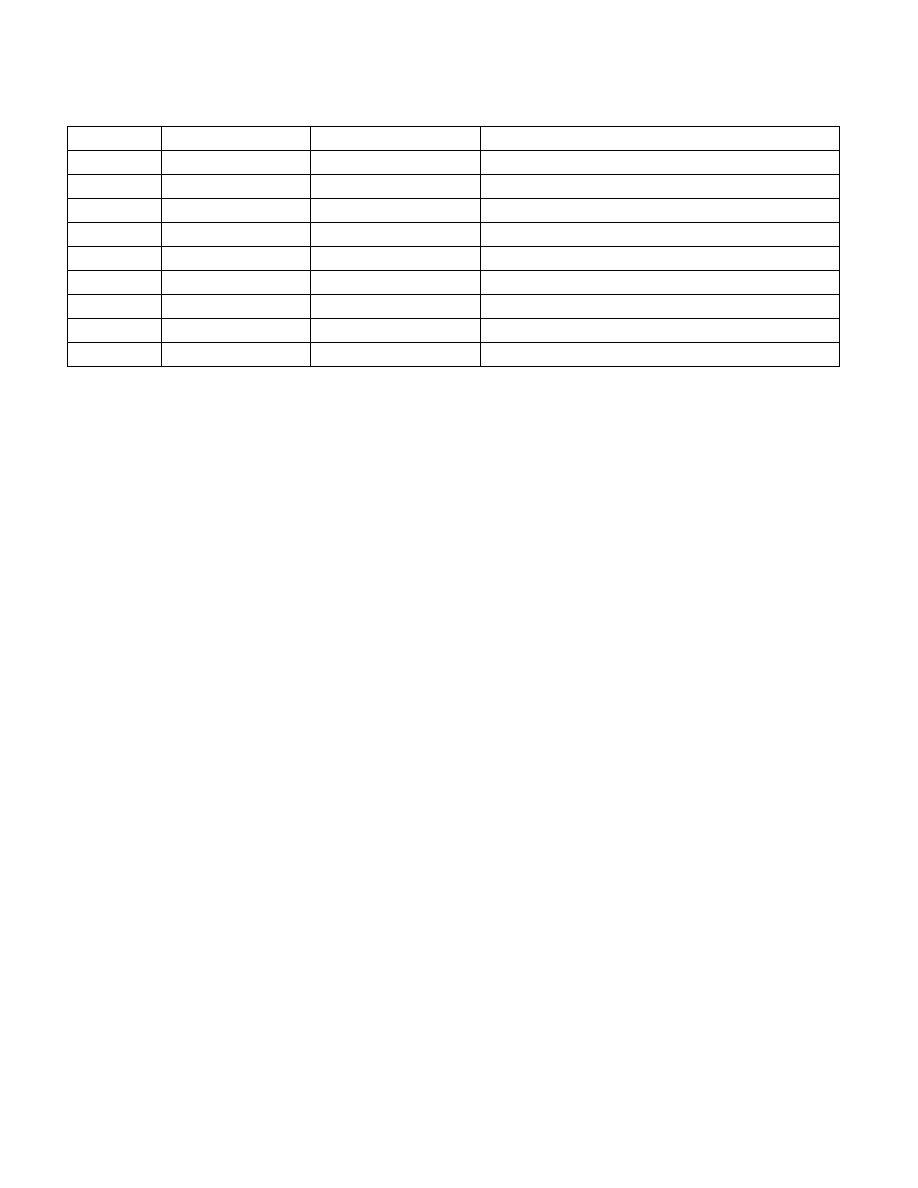

Example 36-1. An Illustrative CYC Packet Example

Time (cycles)

Instruction Snapshot

Generated Packets

Comment

x

call %eax

CYC(?), TIP

?Elapsed cycles from the previous CYC unknown

x + 2

call %ebx

CYC(2), TIP

1 byte CYC packet; 2 cycles elapsed from the previous CYC

x + 8

jnz Foo (not taken)

CYC(6)

1 byte CYC packet

x + 9

ret (compressed)

x + 12

jnz Bar (taken)

x + 16

ret (uncompressed)

TNT, CYC(8), TIP

1 byte CYC packet

x + 4111

CYC(4095)

2 byte CYC packet

x + 12305

CYC(8194)

3 byte CYC packet

x + 16332

mov cr3, %ebx

CYC(4027), PIP

2 byte CYC packet