36-28 Vol. 3C

INTEL® PROCESSOR TRACE

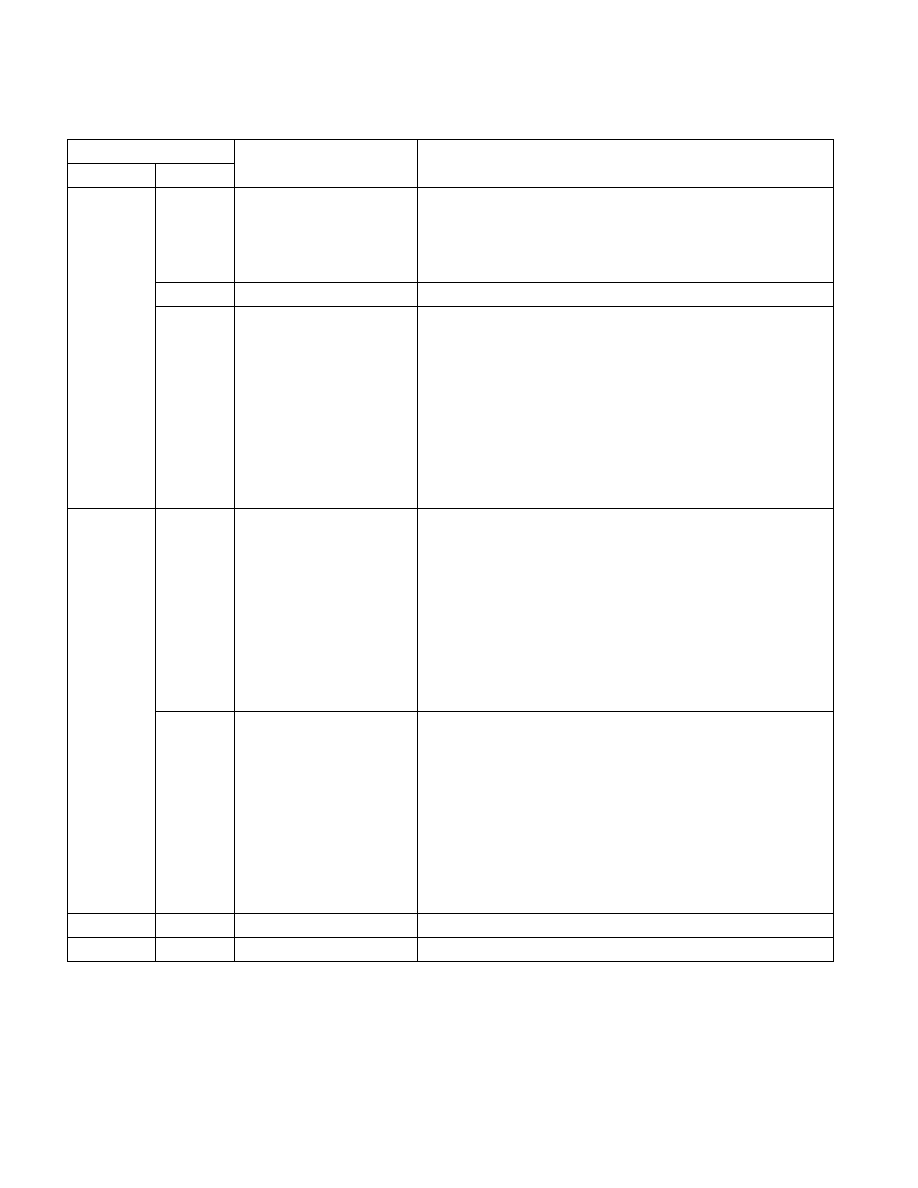

Table 36-12. CPUID Leaf 14H, sub-leaf 1H Enumeration of Intel Processor Trace Capabilities

CPUID.(EAX=14H,ECX=1)

Name

Description Behavior

Register

Bits

EAX

2:0

Number of Address Ranges

A non-zero value specifies the number ADDRn_CFG field supported in

IA32_RTIT_CTL and the number of register pair

IA32_RTIT_ADDRn_A/IA32_RTIT_ADDRn_B supported for IP filtering

and IP TraceStop.

NOTE: Currently, no processors support more than 4 address ranges.

15:3

Reserved

31:16

Bitmap of supported MTC

Period Encodings

The non-zero bit positions indicate the map of supported encoding

values for the IA32_RTIT_CTL.MTCFreq field. This applies only if

CPUID.(EAX=14H, ECX=0):EBX.MTC[bit 3] = 1 (MTC Packet generation is

supported), otherwise the MTCFreq field is reserved to 0.

Each bit position in this field represents 1 encoding value in the 4-bit

MTCFreq field (ie, bit 0 is associated with encoding value 0). For each

bit:

1: MTCFreq can be assigned the associated encoding value.

0: MTCFreq cannot be assigned to the associated encoding value. A

write to IA32_RTIT_CTLMTCFreq with unsupported encoding will cause

#GP fault.

EBX

15:0

Bitmap of supported Cycle

Threshold values

The non-zero bit positions indicate the map of supported encoding for

the IA32_RTIT_CTL.CycThresh field. This applies only if

CPUID.(EAX=14H, ECX=0):EBX.CPSB_CAM[bit 1] = 1 (Cycle-Accurate

Mode is Supported), otherwise the CycThresh field is reserved to 0. See

Section 36.2.7.

Each bit position in this field represents 1 encoding value in the 4-bit

CycThresh field (ie, bit 0 is associated with encoding value 0). For each

bit:

1: CycThresh can be assigned the associated encoding value.

0: CycThresh cannot be assigned to the associated encoding value. A

write to CycThresh with unsupported encoding will cause #GP fault.

31:16

Bitmap of supported

Configurable PSB Frequency

encoding

The non-zero bit positions indicate the map of supported encoding for

the IA32_RTIT_CTL.PSBFreq field. This applies only if

CPUID.(EAX=14H, ECX=0):EBX.CPSB_CAM[bit 1] = 1 (Configurable PSB

is supported), otherwise the PSBFreq field is reserved to 0. See

Section 36.2.7.

Each bit position in this field represents 1 encoding value in the 4-bit

PSBFreq

field (ie, bit 0 is associated with encoding value 0). For each

bit:

1: PSBFreq can be assigned the associated encoding value.

0: PSBFreq cannot be assigned to the associated encoding value. A

write to PSBFreq with unsupported encoding will cause #GP fault.

ECX

31:0

Reserved

EDX

31:0

Reserved