36-26 Vol. 3C

INTEL® PROCESSOR TRACE

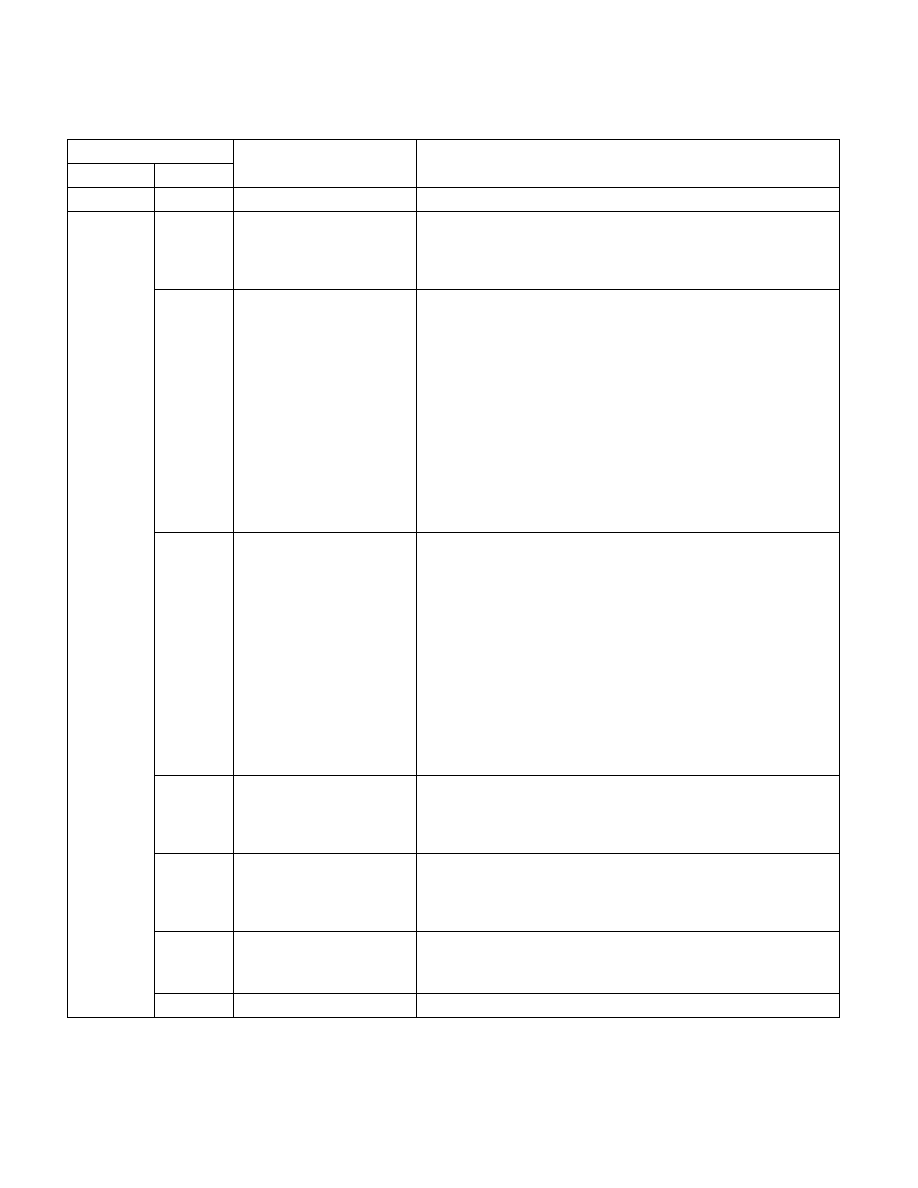

Table 36-11. CPUID Leaf 14H Enumeration of Intel Processor Trace Capabilities

CPUID.(EAX=14H,ECX=0)

Name

Description Behavior

Register

Bits

EAX

31:0

Maximum valid sub-leaf Index Specifies the index of the maximum valid sub-leaf for this CPUID leaf

EBX

0

CR3 Filtering Support

1: Indicates that IA32_RTIT_CTL.CR3Filter can be set to 1, and that

IA32_RTIT_CR3_MATCH MSR can be accessed. See Section 36.2.7.

0: Indicates that writes that set IA32_RTIT_CTL.CR3Filter to 1, or any

access to IA32_RTIT_CR3_MATCH, will #GP fault.

1

Configurable PSB and Cycle-

Accurate Mode Supported

1: (a) IA32_RTIT_CTL.PSBFreq can be set to a non-zero value, in order to

select the preferred PSB frequency (see below for allowed values). (b)

IA32_RTIT_STATUS.PacketByteCnt can be set to a non-zero value, and

will be incremented by the processor when tracing to indicate progress

towards the next PSB. If trace packet generation is enabled by setting

TraceEn, a PSB will only be generated if PacketByteCnt=0. (c)

IA32_RTIT_CTL.CYCEn can be set to 1 to enable Cycle-Accurate Mode.

See Section 36.2.7.

0: (a) Any attempt to set IA32_RTIT_CTL.PSBFreq, to set

IA32_RTIT_CTL.CYCEn, or write a non-zero value to

IA32_RTIT_STATUS.PacketByteCnt any access to

IA32_RTIT_CR3_MATCH, will #GP fault. (b) If trace packet generation is

enabled by setting TraceEn, a PSB is always generated. (c) Any attempt

to set IA32_RTIT_CTL.CYCEn will #GP fault.

2

IP Filtering and TraceStop

supported, and Preserve Intel

PT MSRs across warm reset

1: (a) IA32_RTIT_CTL provides at one or more ADDRn_CFG field to

configure the corresponding address range MSRs for IP Filtering or IP

TraceStop. Each ADDRn_CFG field accepts a value in the range of 0:2

inclusive. The number of ADDRn_CFG fields is reported by

CPUID.(EAX=14H, ECX=1):EAX.RANGECNT[2:0]. (b) At least one register

pair IA32_RTIT_ADDRn_A and IA32_RTIT_ADDRn_B are provided to

configure address ranges for IP filtering or IP TraceStop. (c) On warm

reset, all Intel PT MSRs will retain their pre-reset values, though

IA32_RTIT_CTL.TraceEn will be cleared. The Intel PT MSRs are listed in

Section 36.2.7.

0: (a) An Attempt to write IA32_RTIT_CTL.ADDRn_CFG with non-zero

encoding values will cause #GP. (b) Any access to IA32_RTIT_ADDRn_A

and IA32_RTIT_ADDRn_B, will #GP fault. (c) On warm reset, all Intel PT

MSRs will be cleared.

3

MTC Supported

1: IA32_RTIT_CTL.MTCEn can be set to 1, and MTC packets will be

generated. See Section 36.2.7.

0: An attempt to set IA32_RTIT_CTL.MTCEn or IA32_RTIT_CTL.MTCFreq

to a non-zero value will #GP fault.

4

PTWRITE Supported

1: Writes can set IA32_RTIT_CTL[12] (PTWEn) and IA32_RTIT_CTL[5]

(FUPonPTW), and PTWRITE can generate packets.

0: Writes that set IA32_RTIT_CTL[12] or IA32_RTIT_CTL[5] will #GP,

and PTWRITE will #UD fault.

5

Power Event Trace Supported 1: Writes can set IA32_RTIT_CTL[4] (PwrEvtEn), enabling Power Event

Trace packet generation.

0: Writes that set IA32_RTIT_CTL[4] will #GP.

31:6

Reserved